基于Xilinx FPGA的千兆以太网及E1信号的光纤传输

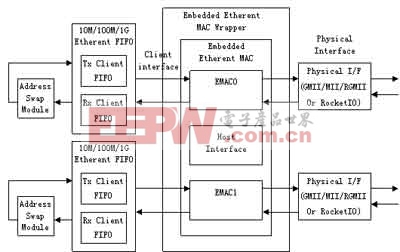

图4 Virtex-5以太网MAC封装的模块结构图

以太网MAC是一个具有162个端口和79个参数的复杂组件。封装文件让你可以仅对特定应用所需端口的参数和接口轻松进行设置。它们的另外一个优势是简化了时钟和物理I/O资源的使用。

以太网MAC封装。在最低级别,实体化一个单独的或者双以太网MAC,同时在CORE Generator GUI中将它的属性设置成你偏好的选项。所有未使用的输入端口接地,未使用的输出端口保持开路状态。

模块级别的封装。在下一层级,对物理接口以及所要求的时钟资源进行实体化。这包括用于串行接口的RocketIO GTP收发器。同时针对你的配置对时钟进行优化,并且利用时钟将输出同步到你的设计。

LocalLink级别的封装。在该级别,将FIFO添加到客户端发送器和接收器接口。FIFO能够处理接收时坏帧的丢失并且以半双工模式对帧重新传输。LocalLink可以作为后端接口使用。

RocketIO GTP Transceiver

RocketIO是一种高速的串行收发器,采用两对差分对来进行数据的发送和接收,可以实现两个单工或一对全双工的数据传输。RocketIO支持622Mb/s~3.75Gb/s的全双工传输速率,还具有8b/10b编解码(平衡编码)、时钟生成及恢复等功能。Aurora协议是为专有上层协议或行业标准的上层协议提供透明接口的第一款串行互连协议,可用于高速线性通路之间的点到点串行数据传输,同时其可扩展的带宽,为系统设计人员提供了所需要的灵活性。

1 PMA和PCS层

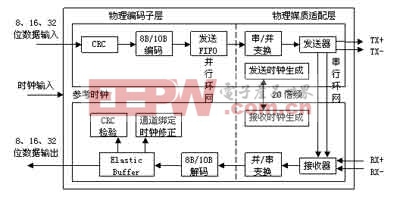

RocketIO包括PMA(物理媒介适配层)和PCS(物理编码子层)两个子层,其内部结构如图5所示。其中PMA子层主要用于串行化和解串,PCS主要包括线路编码和CRC校验编码。

图5 PMA、PCS内部结构框图

PMA子层中集成了SERDES,发送和接收缓冲,时钟发生器及时钟恢复电路。SERDES是一个串并转换器,负责FPGA中本地的32位并行数据(也可以是16位或8位)与RocketIO接口的串行数据之间的转换。采用串行数据收发,可以在高频条件下很好地避免数据间的串扰。时钟发生器及时钟恢复电路用于将时钟与数据绑定发送,以及将时钟从接收到的数据流中恢复出来,从而避免了在高速传输条件下时钟与数据分开传输所带来的时钟抖动等问题。

PCS子层负责8b/10b编码解码和CRC校验,并集成了负责channel绑定和时钟修正的弹性缓冲。8b/10b编码可以避免数据流中出现连0连1的情况,便于时钟的恢复。channel绑定通过在发送数据流中加入P字符来将几个RocketIO通道绑定成一个一致的并行通道,从而来提高数据的吞吐率。最多支持24个通道的绑定。弹性缓冲可以解决恢复时钟与本地时钟的不一致问题,并进行数据率的匹配,从而使得channel绑定成为可能。对Rocket IO模块的配置,可以通过下面两种方式进行:静态特性可以通过HDL代码设置;动态特性可以通过RocketIO的原语端口进行配置。

评论