一种可重构流水线结构模数转换器的设计

摘 要: 设计了一种应用于多标准收发器的可重构流水线结构模数转换器,通过一个重构配置控制信号动态地配置采样频率的大小及分辨率的位数,以满足不同标准及系统的需要。在设计中还采用了共源共栅两级运放和差分动态比较器来优化电路的速度和功耗。仿真结果表明这种可重构流水线结构模数转换器能够很好地实现采样频率及分辨率位数的可重构。

本文引用地址:http://www.amcfsurvey.com/article/189001.htm关键词: 可重构;流水线;共源共栅两级运放;差分动态比较器

随着无线通信技术的快速发展,能够兼容不同通信协议的多标准收发器已经成为当前研究热点之一。而模数转换器(ADC)作为其中的一个重要模块,也受到越来越多的关注。在收发器中不同的接收模式下,系统对模数转换器的采样频率和分辨率位数的要求不同。为了满足系统需要,每一种接收模式都要对应一个特定采样频率和分辨率位数的模数转换器。因此,对于一个存在多种接收模式的多标准收发器[1][2]来说,仅仅在模数转换器方面就需要占用较大的芯片面积及较长的设计时间。

本文主要设计了一种可重构流水线结构模数转换器。该模数转换器通过重构配置控制电路产生一组控制信号来选择不同的流水线级数及时钟信号,从而产生一个采样频率(最高可达50MS/s)和分辨率位数(6~12位)一定的模数转换器。此外在设计中还采用了共源共栅两级运算放大器及差分动态比较器技术来优化电路的速度及功耗。仿真结果表明,这种可重构流水线结构的模数转换器能够自动实现采样频率及分辨率位数(6~12位)的可重构,特别适用于多标准收发器中。

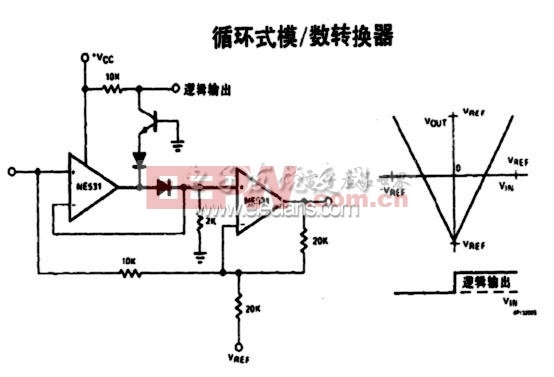

1 可重构流水线ADC的结构

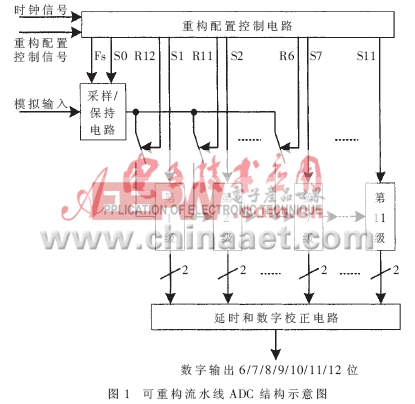

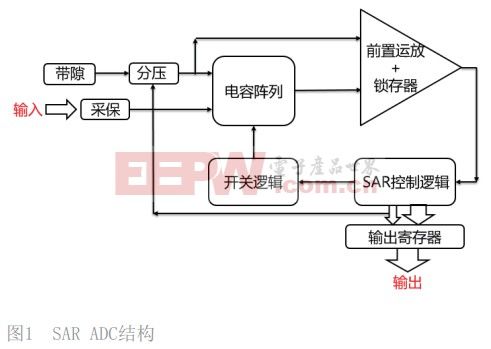

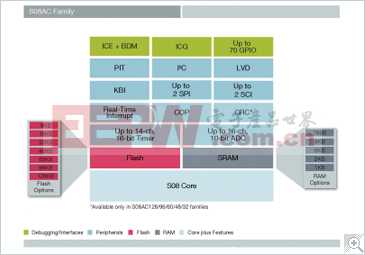

可重构流水线ADC的结构示意图如图1所示,它由一个采样保持电路、11级1.5位/级的流水线、一个重构配置控制电路、延时和数字校正电路等组成;其中前面10级流水线结构完全相同,每级都包括一个2位的子ADC和一个MDAC电路;第11级流水线是一个2位的全并行ADC。

整个可重构流水线ADC的工作原理如下:重构配置控制信号送给重构配置控制电路,重构配置控制电路则根据重构配置控制信号的大小从时钟信号中选择一个时钟频率送给采样保持电路作为采样时钟信号,同时也作为整个ADC的时钟信号。这样,不同的重构配置控制信号就可能选择不同的时钟信号,从而实现ADC采样频率的配置。在产生时钟信号的同时重构配置控制电路也发出一组控制信号S0~S11及R12~R6控制11级流水线的工作状态,其中控制信号R12~R6在ADC工作期间只有一个是处于有效状态,亦即R12~R6所控制的开关只有一个是处于导通状态,其他都断开。由此决定可重构流水线ADC分辨率的位数,并通过S0~S11把没有用到的流水线级数关断,以节省功耗。例如:当R11有效时,ADC的分辨率位数为11位,采样保持电路的输出直接送给第2级流水线作为其输入,同时把第1级流水线关断以节省电路的功耗。当ADC的采样频率和分辨率位数配置之后,整个电路的工作情况就同一般结构的流水线ADC[3]一样,由采样保持电路对输入的模拟信号进行采样,并将保持的采样值送给与之相连的流水线级。接收到采样值的流水线级就对接收到的信号进行转换处理,产生一个2位的数字信号送给延时和数字校正电路,同时产生一个余量增益信号送给下一级流水线作为其输入信号。以此类推,直至最后一级流水线转换完成。各级流水线转换完成后产生的2位数字信号经延时对齐及数字校正后得到最终的数字输出。通过不同的重构配置控制信号,该模数转换器可以实现采样频率(最高可达50MS/s)以及分辨率位数(6~12位)的动态配置,可以满足多标准接收器在不同的接收模式下对采样频率大小及分辨率位数的需要。

2 关键电路设计

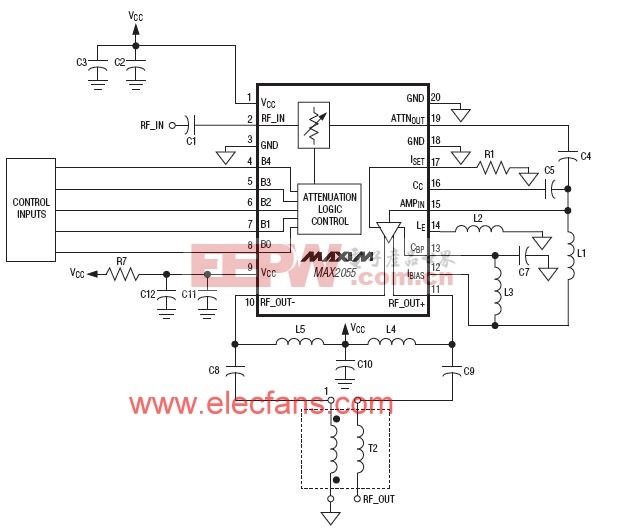

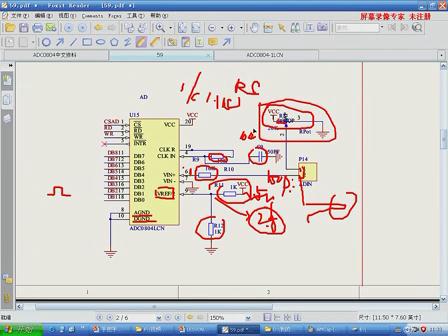

2.1 采样保持电路

评论