基于UART的智能卡接口IP核设计

摘要:分析了UART核的结构和智能卡的传输协议,提出一种基于UART核的智能卡接口IP核的设计。该设计以成熟的UART核为基础,无需编写异步串口的时序与接口逻辑,仅在串口核中增加收发缓冲器和协议处理等模块,减少了工作量并缩短了开发周期。最后对所设计的IP核进行仿真和实际测试,结果表明该IP核设计正确,运行稳定,适合在多卡系统中应用。

关键词:UART;智能卡;IC卡;IP核;FPGA

引言

智能卡以其安全、灵活、通用等特点,被广泛应用在金融、交通以及其他安全终端设备上。目前许多读卡器都采用单片机来实现,而在一些特殊应用中,同时需要多张甚至10张以上的智能卡。由于卡片严格的时序要求,仅用单片机已经很难实现多卡的并行操作。FPGA具有硬件并行性和可编程等优点,很容易实现并行且对时序逻辑要求较高的操作,同时IP核的应用又给基于FPGA的开发带来了极大的便利,能减少大量开发时间。

本文首先介绍了智能卡的基本规范,着重分析字符传输协议(T=0)的操作流程。然后分析了Altera公司提供的UART IP核的结构,在此基础上给出了智能卡接口IP核的设计,并结合智能卡的操作流程,给出了传输协议的状态转换图以及实现方法。最后对IP核进行仿真分析和实际测试。

1 智能卡操作流程简介

智能卡是IC卡的一种,带有微处理器、存储单元以及芯片操作系统,不仅具有数据存储功能,同时还具有命令处理和数据安全保护等功能。智能卡采用异步半双工通信方式,其传输协议分为字符传输协议(T=0)和块传输协议(T=1),本文重点讨论字符传输协议(T=0),它是目前使用较广泛的通信协议。

智能卡主要有复位操作和指令操作。复位操作是将智能卡的复位引脚拉低若干周期,拉高后智能卡回复1个数据帧,提供了协议选择、时钟转换因子、波特率调整因子等参数,可供后续操作使用。该帧的长度在第2个字节中体现,因此先接收2个字节,再接收固定长度的数据,操作流程图如图1所示。

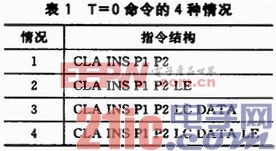

T=0时,指令操作主要有4种情况,如表1所列。

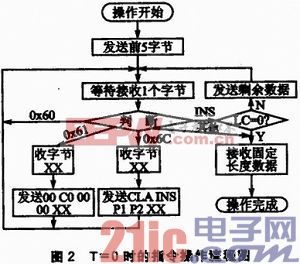

根据中国金融集成电路(IC)卡规范的规定,可在情况1后面补0,组成5字节指令。这时,4种情况都可归纳为:发送前5字节,等待接收1字节回复,由回复决定后续的操作。

1字节的回复分为过程字节和状态字节两类,过程字节主要有INS(或INS补码)、60、61、6C;除过程字节以外的其他回复都属于状态字节。收到过程字节后须执行对应操作。接收到状态字节后须再等待接收1字节状态回复,将两个状态字节上传给控制器,终止本次操作。T=0

时的指令操作流程图如图2所示。

2 智能卡接口IP核的设计与实现

2.1 UART核分析

UART接口已经很成熟,已有许多现成的IP核可使用,利用UART进行智能卡接口IP核的设计可减少大量的开发时间。本文以Altera公司的Avalon总线接口的UART核(下文中所有UART核均指该核)为基础进行设计。

评论