基于FPGA的智能全数字锁相环的设计

1 引言

本文引用地址:http://www.amcfsurvey.com/article/190227.htm数字锁相环 路已在数字通信、无线电电子学及电力系统自动化等领域中得到了极为广泛的应用。随着集成电路技术的发展,不仅能够制成频率较高的单片集成锁相环

路已在数字通信、无线电电子学及电力系统自动化等领域中得到了极为广泛的应用。随着集成电路技术的发展,不仅能够制成频率较高的单片集成锁相环 路,而且可以把整个系统集成到一个芯片上去。在基于FPGA的通信电路中,可以把全数字锁相环

路,而且可以把整个系统集成到一个芯片上去。在基于FPGA的通信电路中,可以把全数字锁相环 路作为一个功能模块嵌入FPGA中,构成片内锁相环

路作为一个功能模块嵌入FPGA中,构成片内锁相环 。

。

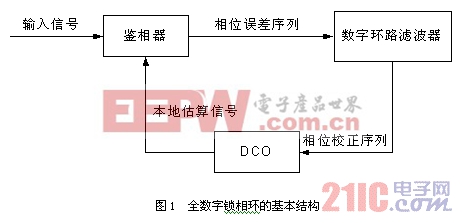

锁相环 是一个相位误差控制系统。它比较输入信号和振荡器输出信号之间的相位差,从而产生误差控制信号来调整振荡器的频率,以达到与输入信号同频同相。所谓全数字锁相环路(DPLL)就是环路部件全部数字化,采用数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)构成的锁相环路,其组成框图见图1示。

是一个相位误差控制系统。它比较输入信号和振荡器输出信号之间的相位差,从而产生误差控制信号来调整振荡器的频率,以达到与输入信号同频同相。所谓全数字锁相环路(DPLL)就是环路部件全部数字化,采用数字鉴相器(DPD)、数字环路滤波器(DLF)、数控振荡器(DCO)构成的锁相环路,其组成框图见图1示。

当锁相环中的鉴相器与数控振荡器选定后,锁相环的性能很大程度依赖于数字环路滤波器的参数设置。

2 K计数器的参数设置

74297中的环路滤波器采用了K计数器。其功能就是对相位误差序列计数即滤波,并输出相应的进位脉冲或是借位脉冲,来调整I/D数控振荡器输出信号的相位(或频率),从而实现相位控制和锁定。

K计数器中K值的选取需要由四根控制线来进行控制,模值是2的N次幂。在锁相环路同步的状态下,鉴相器既没有超前脉冲也没有滞后脉冲输出,所以K计数器通常是没有输出的;这就大大减少了由噪声引起的对锁相环路的误控作用。也就是说,K计数器作为滤波器,有效地滤除了噪声对环路的干扰作用。

显然,设计中适当选取K值是很重要的。K值取得大,对抑止噪声有利(因为K值大,计数器对少量的噪声干扰不可能计满,所以不会有进位或借位脉冲输出),但这样捕捉带变小,而且加大了环路进入锁定状态的时间。反之,K值取得小,可以加速环路的入锁,但K计数器会频繁地产生进位或借位脉冲,从而导致了相位抖动,相应地对噪声的抑制能力也随之降低。

为了平衡锁定时间与相位抖动之间的矛盾,理想的情况是当数字锁相环处于失步状态时,降低K计数器的设置,反之加大其设置。实现的前提是检测锁相环的工作状态。

3 工作状态检测电路

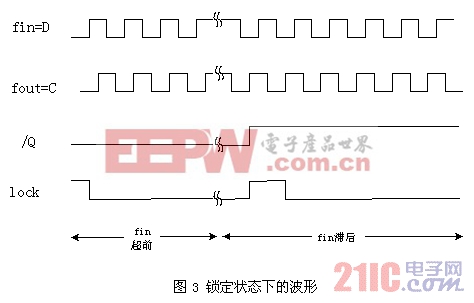

图2为锁相环状态检测电路,由触发器与单稳态振荡器构成,fin为输入的参考时钟,fout为锁相环振荡器输出的时钟移相900。fout对fin的抽样送入单稳态振荡器。

fpga相关文章:fpga是什么

数字通信相关文章:数字通信原理

尘埃粒子计数器相关文章:尘埃粒子计数器原理 鉴相器相关文章:鉴相器原理 数字滤波器相关文章:数字滤波器原理 锁相放大器相关文章:锁相放大器原理

评论