基于FPGA的高速实时数据采集系统设计

摘要:设计的基于FPGA的高速实时数据采集系统,可控制6路模拟信号的采集和处理,FPGA中的6个FIFO对数据进行缓存,数据总线传给DSP进行实时处理和上传给上位机显示。程序部分是用Verilog HDL语言,并利用QuartusⅡ等EDA软件进行仿真,验证了设计功能的正确性。

关键词:FPGA;Verilog HDL;FIFO;数据采集

0 引言

随着当今社会信息技术的快速发展,高速数据采集及处理在人们生活、现代工业和科学研究等很多领域中广泛地应用。同样,在一些高精度、快速的测量中需要对数据进行高质量、高速度的采集。传统的数据采集系统往往采用单片机或数字信号处理器(DSP)作为控制器,来控制模/数转换器(ADC)、存储器和其他外围电路的工作。但由于单片机本身的指令周期以及处理速度的影响,效率较低,很难满足系统对数据采集系统实时性和同步性的要求。同时,FPGA具有高的时钟频率,运行速度快,开发周期短,集成度高,功耗低,设计费用低,组成形式灵活等诸多优点。因此,设计利用FPGA的高速实时数据采集系统有着重要的价值。

1 FPGA硬件设计

1.1 数字系统设计介绍

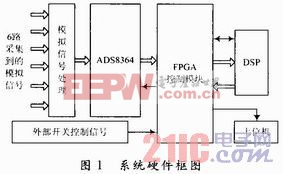

6路模拟信号经过模拟信号处理模块,形成电压差分模拟信号,其目的是减少直流漂移,去除共模干扰,为后级的模/数转换器(ADC)做准备,系统的硬件框图如图1所示。经过ADS8364模数转换器件后,将输入的模拟差分信号变换为适用于控制过程、存储、处理、执行计算并显示读出等其他目的的数字信号。在FPGA的控制下,数字信号被存储在异步FIFO中,再按照设计要求将存储在异步FIFO中的数据通过总线接口实时、高速、大量地传输到DSP芯片中进行实时处理,最后再传输到上位机。

1.2 外围主要电路

1.2.1 外部开关控制信号

外部开关控制信号的作用是给整个系统提供开关信号。为了满足工业应用,避免长线传输中的共地和电平不一致,采用了光电隔离,实现了将输入的24 V电压转化为3 V输出电压的功能,然后再通过整形电路整形后,传输到FPGA的I/O接口上。

1.2.2 A/D转换电路

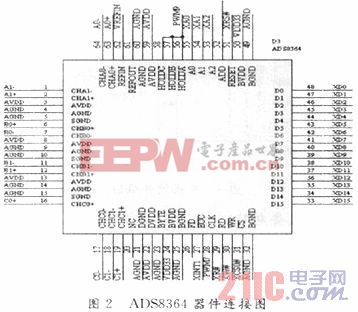

对于采集的6个通道的信号,由于采样速率高,因此选择了ADS8364芯片进行模数转换。其工作电压为+5V,独立6通道全差分输入,2.5V参考电压的REFIN和REFOUT引脚、有效数据位为14位、采样频率可以根据设计要求进行调节并且最高的采样频率可以达到250 KSPS、带有6级深度的FIFO输出、功耗只有450 MW、6个差分采样放大器以及高速并行接口等主要参数。

ADS8364芯片的输入通道分为三组(A,B和C)的6路模拟信号输入通道,每个端口含有ADCS和保持信号引脚,这两个信号用来保证几个通道能同时进行采样和转换,同时输入电压是从-VREF到+VREF之间变化的差分模拟输入电压信号。6个十六位ADCS可以同时工作,即6通道同时进行转换。HOLDA,HOLDB,HOLDC这三个转换保持信号启动相对应的通道进行模数转换。如果这些保持信号同时有效时,这6个通道转换的结果就被保存在6个寄存器中,如果FPGA中的AD控制模块对ADS8364芯片执行每一个读操作时。ADS836就会输出十六位数据到FPGA中,A0,A1,A2这3个是地址/模式信号,它们决定ADS8364芯片采用何种方式读取数据。有单通道,单周期或FIFO模式三种模式供选择。HOLDA,HOLDB,HOL DC至少20 ns保持低电平,相应的通道才能开始转换。20 ns的低电平使得相应通道的采样保持放大器处于保持状态,进而所选择的模数转换通道就开始进行数据转换,本设计方案所选择的ADS8364地址/模式信号是单通道模式读取数据,6通道同时进行数据转换,其器件连接图如图2所示。

1.2.3 UART通信模块

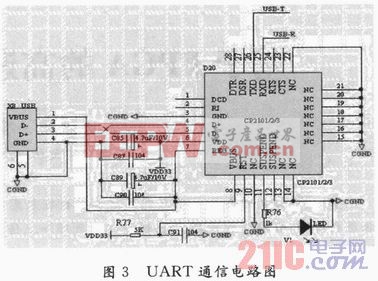

在本设计中,采用了一片CP2101芯片来实现与PC机的USB接口通信,其电路原理图如图3所示。

评论