端接电路的串扰分析

图6.16中,相邻的端接电路会在电路走线之间交叉耦合信号能量。这种交叉耦合比通常发生在相邻传输线之间的串扰更严重。

本文引用地址:http://www.amcfsurvey.com/article/190874.htm

本文将提供接交叉耦合的实际测量结果,同时给出了一些预测端接电路串扰的提示。

端接中的串扰同时来自互感耦合和互容耦合。感性耦合通常比较大,总耦合是感性部分和容性部分的总和,这两部分都与输入信号的导数成正比。我们的目的是找到一个总耦合系数,而不关心安到底是磁场还是电场的耦合。

其中:噪声电压=耦合到走线2的峰值串扰

K=交叉耦合系数

R=阻抗,Ω

△V=驱动信号阶跃幅度,V

T10~90%=驱动信号上升时间,S

1、相邻实芯电阻的串扰

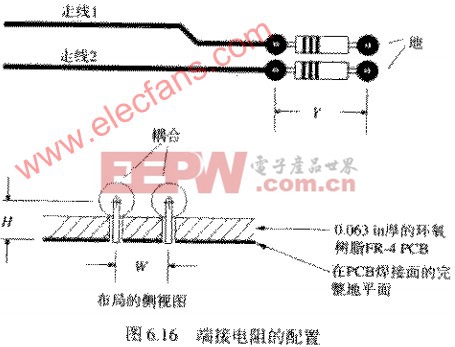

端接电阻相邻插装的感性耦合通常依照上式的规则。我们可以用这个近似式来方便地估算串扰系数:

其中,Y=两个插孔之间电阻的长度,IN

H=到地平面的中心线的高度,IN

W=电阻中心线之间的间距,IN

K=串扰耦合系数

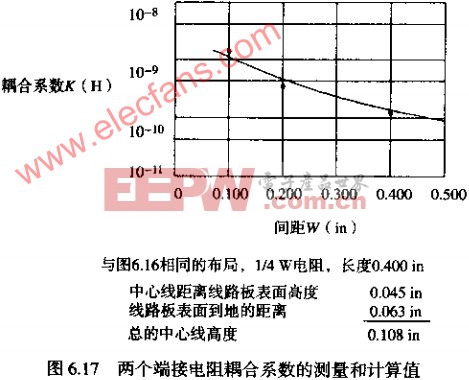

图6.17绘出K的测量值和计算值,测量值是从一个实际例子中测量出的真实串扰,然后采用式()推算出K值,计算值是从上式得出的,采用与实际例子中相同的长度和高度,但间距不同。

评论