印刷电路板叠层方法

印刷电路板的叠层用于具体说明电路板层的安排。它详细指定了哪一层是完整的电源和地平面,基板的介电常数以及层与层的间距。当规划一个叠层的时候,也要计算走线尺寸和最小走线间距。

本文引用地址:http://www.amcfsurvey.com/article/190878.htm生产限制会严重地影响叠层,通常,电路的走线密度越大,每一英雨的生产成本就会越高。

本文将详述规划叠层的一些基本的经验法则。

1、电源和地的规划

首先设计电源和地层。规划一个电源和地系统时,首先要确定信号的上升时间,信号的数量,以及电路板的物理尺寸。

在物理尺寸中包括推测走线的宽度。在这一阶段,走线宽度的假设并不是特别严格。

下一步,利用完整的、平行的和指状的地平面模型估计自感和互感。此时,通过已经清楚了哪个模型更适合设计。注意,对于指状的地模型,所有的走线都相互影响。此时通常已经清楚了哪个模型更适合设计。注意,对于指状的地模型,所有的走线相互影响。对于平行的模型,沿着同一平行栅格由放的走线相互影响。对于完整的地平面模型,只有相邻的走线相互影响。

如果要使用一个完整的地平面,应安排地和电源平面成对使用。在一个叠层设计中,完整平面对称使用。可以帮助避免电路板的变形。如果一个板子只有一个完整平面,偏一侧,则将使板子明显变形。

如同地平面一样,电源平面可以作为信号返回电流的低电感路径。假设在电源和地之间有足够的旁路电容,传输线跃起在电源平面上的布线,与电源地平面上的布线方法相同。带状传输线的布线可以在一个电源层和一个地层之间,或在两个电源层之间。

2、机框层

有时候需要在数字系统之外走一个信号。对于这种应用,可以选择一个低速或上升时间受控的驱动器。这是一个好的选择,因为它减少了外部的辐射,对于满足FCC的规定会有所帮助。

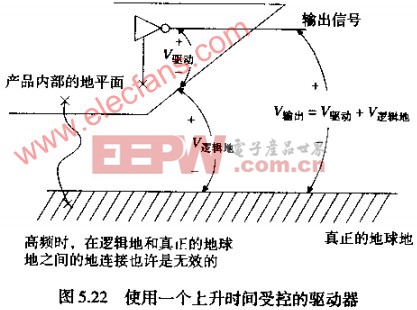

如果驱动器的地连接到通常的数字逻辑地上,有效的驱动输出等于它的设计驱动电压加上任何出现在数字逻辑地上的噪声电压,如图5.22所示。

众所周知,数字逻辑地的高频噪声电压非常严重。地传递的波动电压是由许多返回信号电流通过它们的自感引起的。对于数字电路,这些高频波动很小,不足以产生问题,但是大大超过了FCC的限度。任何引出机壳的线,如果连接到数字逻辑地,在FCC测试时几乎总是失败的。

如果没有其他的预防手段,上升时间受控的驱动器会显著地拾取地噪声并在机箱外广播。

解决这个问题的一种方法是在叠层中加入一个机框平面。这一平面紧贴一个接地平面,使时间受控的驱动器附近,沿着一个连续的轴线,将机械平面通过螺丝钉焊接或熔接到外部机框,在高频部分,我们已经有效地把数字接地一面短接到机框。这样,在这个点上就减少了数字噪声的数量,也减少了上升时间受控的驱动器传到外部的噪声。

因为普通电容的引脚电感太大,所以不能用它们实现机框地和数字地之间的短路功能。只有在机框平面和数字地平面之间有非常大的宽而平行的表面面积,才有足够低的电感,从而有效地把两个平面答非所问在一起。

采用机框平面方式,在低频部分,数字逻辑和外部的机框保持着隔离,对于安全或其他方面,这都是非常必要的,如果隔离无关紧要,简单地直接把数字逻辑地短接到机框即可,而不必使用一个单独的机框层。

连接过程可以沿着受控的驱动附近的连续轴线,通过螺丝钉焊接或熔接到外部机框来完成。

当使用一个机框平面的时候,在叠层中要和其他一些完整平面均衡使用。因为机械原因,在叠层中总是倾向于对称地安排平面。

评论