基于FPGA软核的高速数据采集系统设计

数据采集在现代工业生产及科学研究中的重要地位日益突出,同时对实时采集、实时传输、实时处理的高速数据采集的要求也不断提高。此外,对于不同的场合,数据采集系统的数据采样参数要求也不同。工业生产与科研领域中对数据采集研发提出了以下的要求:(1)接口简单灵活且有较高的数据传输率;(2)采集器体积小、抗干扰能力强、能够对数据做出快速的存储,并及时进行分析和处理;(3)设计周期短,能快速适应市场需求。

USB2.0以其即插即用、支持热插拔的灵活性,以及高达480 Mb/s的传输速率,成为了高速数据传输接口的首选。而FPGA以其工作频率和集成度高、稳定性良好、抗干扰能力强等优点,逐步成为各领域数据采集数字电路的首选。FPGA集成软核有设计周期短、设计投入少等优越性,且不涉及具体的物理实现,可以方便移植到各种FPGA硬件平台,极大提高了它的灵活性和适应性。

1 系统方案与结构

数据采集系统性能指标修改主要集中在A/D转换模块与FPGA控制模块上,在USB2.0接口的硬件、固件、驱动程序的设计以及PC机应用软件的设计基本没有变化。而A/D转换模块的修改可以通过A/D转换芯片的选择及更改输入信号调理电路设计来实现。但更换不同的A/D转换芯片可能给A/D转换的启停控制、数字信号的缓存等方面带来较多的改动。而FPGA软核的模块化设计可以极大地减少这方面的改动。

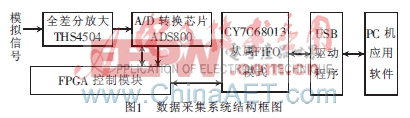

本文以TI公司的低功率高性能A/D转换芯片ADS800为例介绍系统的设计。图1为本数据采集系统的结构框图。模拟信号经过THS4504全差分放大器进行信号差分放大后,输入到ADS800进行A/D转换。为减少不同系统中FPGA软核改动的工作量,FPGA内部按功能设计了三个软核作为系统的控制单元。CY7C68013作为USB控制芯片设置为从属FIFO模式(Slave FIFO Mode),负责数字信号在采集系统与PC机间的传输;用户通过LabVIEW设计的PC机应用软件,在驱动程序的驱动下与数据采集系统进行命令以及数据的传输,以便对数据采集系统采集到的数据进行实时处理。

2 系统硬件设计

2.1 模数转换电路

数据采集系统采样参数调整的本质在于模数转换电路的改变,设计者只需要更换不同的A/D转换芯片、重新设计其硬件电路即可达到目标。本系统中模数转换电路由信号调理电路与高速A/D转换器组成。信号调理电路负责对待测模拟信号进行差分放大,高速A/D转换器负责模拟信号到数字信号的转换。

为了能精确检测微弱信号,数据采集系统的ADC前加入了全差分放大器THS4504,采用ADS800作为A/D转换芯片。ADS800含12 bit流水线型A/D转换内核,支持差分输入,最高转换速率高达40 MHz[1],极好地满足了本系统采样频率的要求。

2.2 FPGA芯片外围电路

本系统FPGA采用Xilinx公司的XC3S200AN-4-FT256-C芯片。该芯片拥有20 万门逻辑单元,内含16 个18 KB的块存储器(Block RAM)与30 KB分布存储器(Distributed RAM),最高工作频率达到326 MHz[2],可满足本系统的时序需求。

FPEA芯片外围电路:

(1)FPGA与A/D接口模块

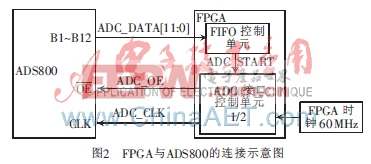

ADS800的控制信号由FPGA生成,ADS800的转换时钟设定为30 MHz,由FPGA的时钟分频获得。FPGA与ADS800的连接示意图如图2所示。本设计中,FPGA通过ADC_OE来控制ADS800转换数据输出的启停;ADS800的30 MHz工作时钟由FPGA的60 MHz工作时钟经过二分频得到;ADS800的数据由并口输出,FPGA内部FIFO控制单元将接收到的12 bit数据转换成16 bit数据存入FPGA内的FIFO中。

当更换不同的A/D转换芯片时,A/D转换芯片与FPGA的连接有所不同。但对于并行输出、流水线型的A/D转换芯片,只需模仿上述连接方式,对输出位数、控制时序以及FPGA时钟分频大小等做合适的修改即可。

(2)FPGA与USB接口模块

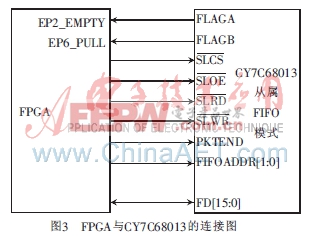

本设计中使用Cypress公司生产的EZ-USB FX2LP系列的CY7C68013芯片作为USB2.0协议的微控制器芯片。由于该芯片支持480 Mb/s高速传输,为本设计数据传输提供了速率保证。FPGA与CY7C68013的连接图如图3所示。

FLAGA、FLAGB脚可通过PINFLGSAB、PINFLAGSCD寄存器来选择其工作在索引模式还是固定模式。本设计中被设置为固定模式。其中FLAGA表示EP2的空状态(FIFO_EMPTY),FLAGB表示EP6的满状态(FIFO_FULL)。

2.3 USB接口外围芯片电路

本设计使用容量为16 KB的EEPROM芯片AT24C016A存储,并设置CY7C68013的VID与PID。在CY7C68013上电并脱离复位状态后,内部逻辑会检查I2C端口上是否连接有串行EEPROM。如果有,则判断连接上的EEPROM第一个字节是0xC0还是0xC2。本设计中设置EEPROM第一个字节为0xC0,设置VID=0x1234、PID=0x2211、DID=0x0001。在这种情况下,由CY7C68013内核提供USB描述符,使用EEPROM存储的VID/PID/DID值替换CY7C68013内部的值,并设置RENUM=0。这样,在设备重新列举后,芯片内的程序代码会以全新的自定义设备来加以呈现。

3 FPGA软核设计

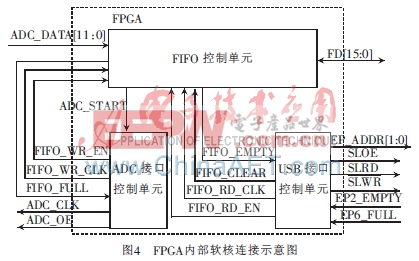

FPGA内部控制单元的功能分别由三个软核负责完成,分别为:ADC接口控制单元、FIFO控制单元以及USB接口控制单元。三个软核连接示意图如图4所示。

3.1 ADC接口控制单元

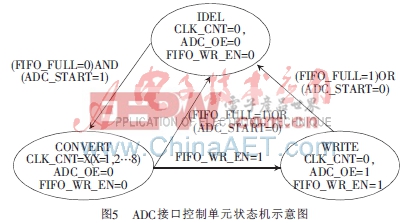

ADC接口控制单元控制数据采集的启停和传输。数据采集开始时,ADC接口控制单元将时钟信号分频为30 MHz供ADS800作转换时钟ADC_CLK使用。此时控制单元内寄存器CLK_CNT对ADC_CLK转换时钟进行周期计数,当经过7个时钟周期后(ADS800转换延时为6.5个时钟周期,为了使转换数据稳定,本设计再延时半个时钟周期输出)即CLK_CNT=8时,CLK_CNT清零,FIFO写时钟(FIFO_WR_CLK)输出,同时端口FIFO_WR_EN置高电平,经ADC转换完成的数据在补齐16 bit后,随时钟FIFO_WR_CLK上升沿存入FIFO中。ADC接口控制单元状态机工作过程如下:

(1)当FPGA上电或者复位后,状态机进入空闲状态(IDEL)。

(2)在空闲状态下,当FIFO不满(FIFO_FULL=0)且ADC_START=1时,状态机进入转换状态(CONVERT),此时,ADC_CLK输出ADC数据转换时钟。

(3)在转换状态下,当FIFO_WR_EN=1,即数据转换延时结束时,状态机进入写状态(WRITE),此时CLK_CNT清零,ADC_OE和FIFO_WR_EN都置为高电平,FIFO_WR_CLK输出FIFO写时钟。

(4)在任何状态下,如果FIFO已经写满(FIFO_FULL=1)或者ADC_START=0时,自动跳转到空闲状态。

ADC接口控制单元状态机示意图如图5所示。

3.2 FIFO控制单元

本设计首先使用FPGA内部Block RAM生成FIFO。由于A/D接口控制单元输出数据宽度为16 bit,因此,FIFO宽度也设置为16 bit,深度设置为4 KB。FIFO可以使用Xilinx ISE套件中的Core Generator生成器,由Core Generator生成的FIFO软核配合控制部分构成FIFO控制单元。FIFO控制单元内部结构示意图如图6所示。

由于本设计中数据采集系统处于异步从属FIFO模式,且USB接口芯片读数据的速度与ADC数据写入FIFO的速度不同。为解决因读写速度不同而可能带来的数据读写错误问题,FIFO软核上的FULL与EMPTY两信号线可以分别指示FIFO满与空的状态。当FIFO处于满状态时,FIFO_FULL信号置高电平,由ADC控制单元通知ADC停止采集数据;当FIFO处于空状态时,FIFO_EMPTY信号置为高电平,由USB接口控制单元通知USB接口芯片停止读FIFO。FIFO的读时钟信号(FIFO_RD_CLK)与读使能信号(FIFO_RD_EN)由USB接口控制单元提供,写时钟(FIFO_WR_CLK)与写使能信号(FIFO_WR_EN)由ADC接口控制单元提供。FIFO控制单元的工作有以下两种特殊情况:

评论