利用 IDDR 简化亚稳态

如果在具有多个时钟的非同步系统中使用FPGA,或者系统中的时钟频率或相位与FPGA所使用时钟频率或相位不同,那么设计就会遇到亚稳态问题。不幸的是,如果设计遇到上述情况,是没有办法完全解决亚稳态问题的,不过还是有一些方法可降低系统出现亚稳态问题的几率。

本文引用地址:http://www.amcfsurvey.com/article/191462.htm

先来深入研究一下引起亚稳态的原因,再谈谈用哪些方法加以应对。

什么是亚稳态

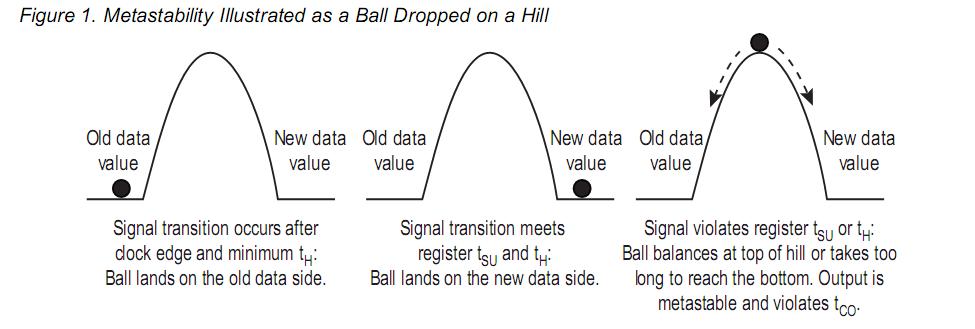

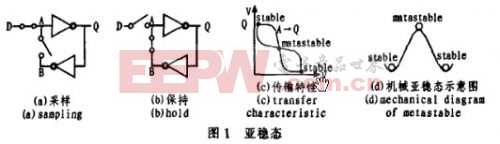

在FPGA等同步逻辑数字器件中,所有器件的寄存器单元都需要预定义信号时序以使器件正确地捕获数据,进而产生可靠的输出信号。当另一器件将数据发送给FPGA时,FPGA的输入寄存器必须在时钟脉冲边沿前保证最短的建立时间和时钟脉冲边沿后的保持时间,从而确保正常完整地 接收信号。

在一定的延迟后,寄存器输出端随后将信号发送到FPGA的其他部分。不过,如果信号传输违反了指定时间要求,那么输出寄存器可能就会进入所谓的亚稳态,这就导致寄存器输出值会在高低状态之间波动,且这种状态的时间不确定,从而使稳定输出状态无法达到寄存器指定的时间,进而造成性能略有延迟或逻辑行为的副效应。

解决问题

一般来说,将FPGA连接到另一个具有不同时钟域的数字器件时,必须给FPGA的输入部分添加一级同步,使FPGA时钟域中的第一个寄存器充当同步寄存器。为了实现这一目的,可在FPGA器件的输入级中使用一系列寄存器或同步寄存器链。该链可在输入寄存器将信号发送到FPGA的其他区域之前,允许 能有更多的时间解决潜在的亚稳态信号问题。亚稳态信号的稳定时间通常比一个时钟周期要短得多,因此即便延迟半个时钟周期,亚稳态出现的概率也会按数量级减少。

为了降低亚稳态问题的出现概率,在设计中实现的一系列寄存器(连接成移位寄存器)必须满足以下标准要求:

所有寄存器必须由同一时钟,或与同一时钟相位相关的时钟控制。

链中每个寄存器的扇出都仅针对相邻的寄存器。

由于不能完全消除亚稳态问题,因此必须做好解决问题的准备。为此,设计人员采用平均故障间隔时间(MTBF)这个指标来估算从问题出现并导致故障的两个事件间的平均时间。MTBF值越高,说明设计的稳定性越高。如果发生了“故障”,只是说明没有解决亚稳态问题,并不是系统本身真的出现了故障。

如欲了解测量亚稳态的方法,敬请访问:http://www.xilinx.com/support/documentation/application_notes/xapp094.pdf,查阅赛灵思应用指南XAPP094。

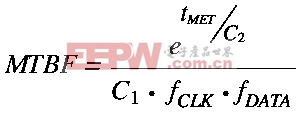

可用以下方程式计算出寄存器的MTBF:

在本例中,C1和C2代表寄存器技术相关常数,tMET代表亚稳态的稳定时间。

可根据每个寄存器的MTBF,确定总的MTBF值。同步器的故障率为1/MTBF,则将每个同步器的故障率相加,就能计算出整个设计的故障率:

从上式可以明显看出,通过改进寄存器单元的架构,优化设计以延长同步寄存器的tMET,甚至增加链中寄存器的数量等多种方法来改进MTBF。

高层代码与布局图

如果发现输入信号存在潜在的亚稳态问题,只需创建与同一时钟有相位关系的时钟驱动的寄存器链就能解决此问题。这需要提供如图1所示的电路。

评论