基于FPGA的卷积编译码器的设计与实现

摘要:为了解决传统的维特比译码器结构复杂、译码速度慢、消耗资源大的问题,提出一种新型的适用于FPGA特点,路径存储与译码输出并行工作,同步存储路径矢量和状态矢量的译码器设计方案。该设计方案通过在ISE9.2i中仿真验证,译码结果正确,得到编码前的原始码元,速度显著提高,译码器复杂程度明显降低。并在实际的软件无线电通信系统中信道编解码部分得到应用,性能优良。

关键词:卷积码;维特比;FPGA;软件无线电(SDR)

卷积码是Elias在1955年最早提出的,稍后,Wozencraft在1957年提出了一种有效译码方法,即序列译码。Massey在1963年提出了一种性能稍差,但比较实用的门限译码方法,由于这一实用性进展使卷积码从理论走向实用。而后Viterbi在1967年提出了最大似然译码法,该方法对存储器级数较小卷积码的译码很容易实现,并具有效率高、速度快、译码器简单等特点,人们后来称其为维特比算法或维特比译码,广泛应用于现代通信中。本文主要论述了基于Xilinx公司的FPGA的卷积编码器及相应的维特比译码器的研究,并在幸存路径存储与译码输出判决方面提出了改进算法,从而使译码器结构得到简化。

1 卷积码的编码原理与实现

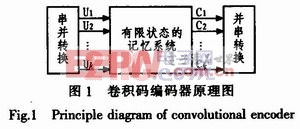

卷积码是一种重要的前向纠错编码FEC,用(n,k,m)表示。分组码不同,其监督元与本组的信息元和前若干组的信息元有关。这种编码的纠错能力强,不仅可纠正随机差错,而且可纠正突发差错。卷积码根据需要,有不同的结构及相应的纠错能力,但都有类似的编码规律。卷积码的编码器是一个具有k个输入位(端)、n个输出位(端),m级移位寄存器的有限状态记忆系统。通常称为时序网络。其中R=k/n为编码效率,m为约束长度。卷积码编码原理如图1所示。

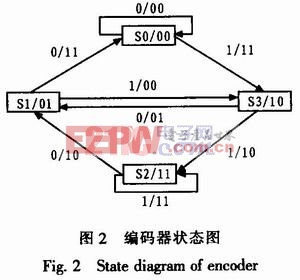

卷积编码充分利用各组信息元之间的相关性,在误码率和复杂度相同的情况下性能优于分组码,并且最佳译码更易实现,因此在通信系统中得到广泛应用。但是卷积码没有严格的代数结构,尚未找到严密的数学手段将纠错性能与码的构成有规律地联系起来,目前大都采用计算机搜索好码。通常是(2,1,3)卷积码,本文以生成多项式G=(111,101)的(2,1,3)卷积码为例介绍设计和实现过程。

设初始状态为SO编码为00,根据生成矩阵分别带入输入O和输入1时得到下一个状态和相应输出。依次代入,可得到如图2所示的状态图。

评论