基于FPGA的数字幅频均衡功率放大器的解决方案

摘要:提出了一种基于FPGA 的数字幅频均衡功率放大器的设计方案。系统在完成基于AD620前级小信号放大电路设计的基础上,分析了阻带网络的幅频特性;结合分析结果与FIR 滤波算法给出了相应的滤波器组成方案。后级功率放大电路采用分立MOS 管实现。

本文引用地址:http://www.amcfsurvey.com/article/191486.htm在现代通信系统中,码间干扰是制约通信质量的重要因素。为了减小码间干扰,需要对信道进行适当的补偿,以减小误码率,提高通信质量,接收机中能够补偿或减小接收信号码间干扰的补偿器称为均衡器。。本文提出了一种基于FPGA 的数字幅频均衡功率放大器的解决方案。

1 系统总体设计

本文设计了一种数字信号幅频均衡功率放大器的实现方案。设计主要由四个模块组成。分别为小信号放大,带阻网络衰减,数字信号幅度的均衡处理以及功率放大。其中小信号放大部分由精密度高、噪音系数小的运算放大器AD620 实现;数字信号处理部分以FPGA 为处理核心,辅助以A/D、D/A 模块进行模拟信号和数字信号的转换;末级功放电路采用分立的MOS管来实现。

2 硬件电路设计

2.1 前置放大电路设计

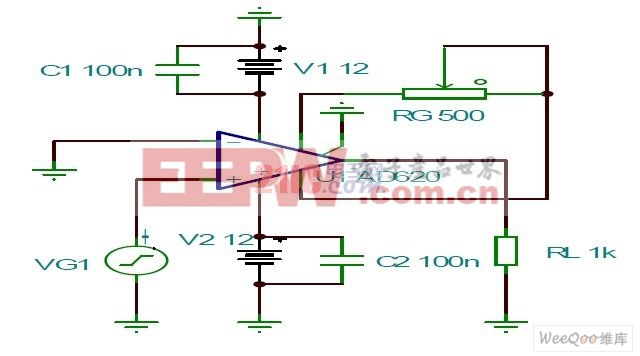

前置小信号放大器利用低功耗高精度的仪表运放AD620[3],在运放1 管脚和8 管脚之间介入可变电阻来实现增益可控,以满足题目中要求放大倍数不小于400 倍。前级放大电路如图1所示。根据AD620 的内部结构,其增益表达式如下:

Au=(R1+R2)/RG+1=49.4k Ω / RG+1,其中,RG 的单位为k Ω 。

图1 AD620 放大电路

2.2 带阻网络的计算

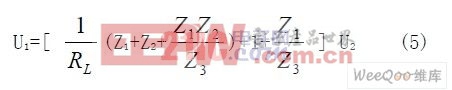

阻带网络电路(详见赛题)。根据基尔霍夫定律:

I1=I2+I3 (1)

U1= I1Z1+I3Z3 (2)

I3Z3= I2Z2+ U2 (3)

U2= I2RL=600*I2 (4)

由式(1)(2)(3)(4)得U1 、U2 的关系:

(其中,Z1、 Z2 、Z3 分别为各谐振网络的总阻抗)

评论