基于FPGA的移位寄存器流水线结构FFT处理器设计与实

快速傅里叶变换(FFT)在雷达、通信和电子对抗等领域有广泛应用。近年来现场可编程门阵列(FPGA)的飞速发展,与DSP技术相比,由于其并行信号处理结构,使得FPGA能够很好地适用于高速信号处理系统。由于Altera等公司研制的FFT IP核,价钱昂贵,不适合大规模应用,在特定领域中,设计适合于自己领域需要的FFT处理器是较为实际的选择。

本文设计的FFT处理器,基于FPGA技术,由于采用移位寄存器流水线结构,实现了两路数据的同时输入,相比传统的级联结构,提高了蝶形运算单元的运算效率,减小了输出延时,降低了芯片资源的使用。在OFDM系统的实际应用中,因它可以采用快速傅里叶变换,能方便快捷地实现调制和解调,故结合MIMO技术,设计的FFT处理器结构,可以很好地应用于2根天线的MIMO-OFDM系统中。

1 FFT处理的应用及DIF FFT算法原理

图1给出一个2根天线MIMO-OFDM系统中FFT的使用。快速傅里叶变换算法基本上分为两大类:时域抽取(DIT)和频域抽取(DIF),这里设计的FFT处理器采用基-2 DIF算法。

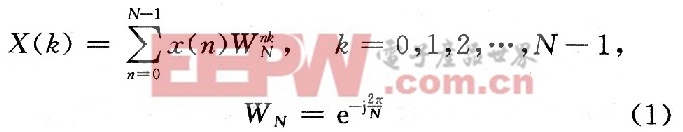

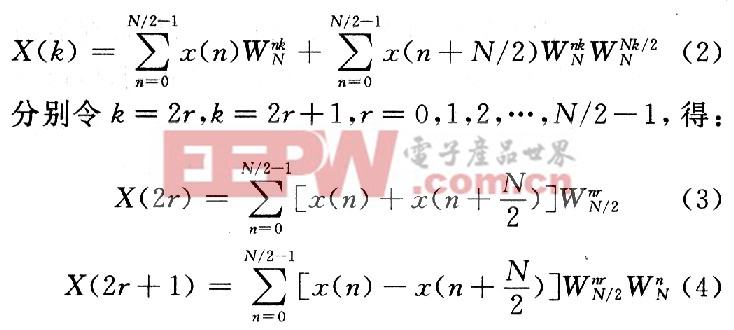

对于N点序列x(N),其傅里叶变换

将x(n)分成上、下两部分,得:

这样将两个N点的DFT分成两个N/2点的DFT,分的方法是将x(k)按序号k的奇、偶分开。通过这种方式继续分下去,直到得到两点的DFT。采用DIF方法设计的FFT,其输入是正序,输出是按照奇偶分开的倒序。

2 移位寄存器流水线结构的FFT

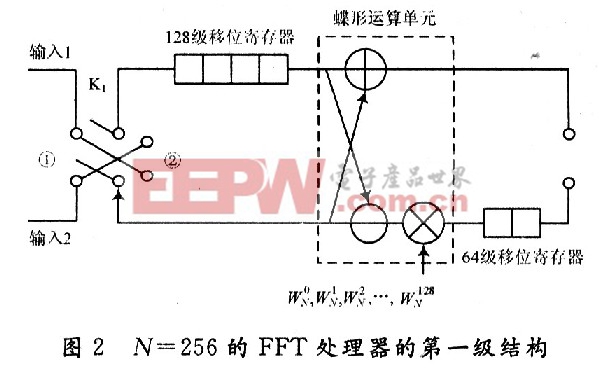

在传统流水线结构的FFT中,需要将全部数据输入寄存器后,可开始蝶形运算。在基-2 DIF算法中可以发现,当前N/2个数据进入寄存器后,运算便可以开始,此后进入的第N/2+1个数据与寄存器第一个数据进行蝶形运算,以此类推。

由于采用频域抽取法,不需要对输入的数据进行倒序处理,简化了地址控制,这样,可以采用移位寄存器的方式,依次将前N/2个数据移入移位寄存器,在N/2+l时刻,第一个数据移出移位寄存器,参与运算。相对于传统的RAM读写方式,采用移位寄存器存储结构综合后的最大工作频率为500 MHz,远大于RAM方式的166 MHz。

当移位寄存器相继有数据移出时,在移位寄存器中会出现空白位。此时,引入第二路数据,在第一路数据依次移出进行蝶算时,第二路数据依次补充到移位寄存器的空白位中,为运算做准备。通过这样一种类似“乒乓操作”的结构,可以使蝶形运算模块中的数据不间断地输入,运算效率达到100%。不同于传统的“乒乓操作”结构,由于使用移位寄存器,不需要两块RAM,可以省掉一半的寄存器。图2为256点FFT处理器的第一级结构。

评论