GNSS接收机中数据传输优化方法设计与应用

摘要:对于基于FPGA+DSP架构实现的、需要同时接收处理多系统多频点导航卫星信号的GNSS接收机,随着跟踪通道数目成倍增长以及为提升抗多径等性能造成的每通道相关器数目的增加,FPGA和DSP之间需要交互的相关值数据量也将成倍增加。本文在定制的FPGA+DSP的硬件平台上,利用DSP芯片的QDMA功能,消除了连续数据读取间隔的无效时间,并实现了卫星信号处理与相关值数据传输的并行化,显著降低了数据传输对DSP处理时间的占用,使得在同样硬件平台上跟踪通道数由44个提高到96个,满足了项目设计的要求。

本文引用地址:http://www.amcfsurvey.com/article/201610/306158.htm引言

随着北斗导航卫星系统(BDS)、伽利略导航卫星系统(Galileo)以及Glonass导航卫星系统的发展,全球导航卫星系统(Global Navigation Satellite Systems,GNSS)接收机工作模式已经从单模单频向多模多频转变,这一趋势在高精度卫星导航接收机以及兼容互操作接收机中体现得更加明显。接收信号数量的增加直接导致接收机通道数量的成倍增加。同时,为了提升抗多径干扰的能力,接收机相关通道通常在典型的三组复相关器的基础上额外增加两组复相关器。此外,为了适应新信号体制下的导频分量与数据分量的同时接收,接收机相关通道内部需要单独一路相关器对数据支路进行数据解调。接收机通道数据增加以及相关器数量的增加直接导致DSP与FPGA之间传输数据量的剧增。

DSP与FPGA之间的通信通常采用EMIF异步总线方式实现,由于传输数据量的成倍增加,数据传输所占用的CPU时间也将成倍增加,最终导致CPU不能在0.505mS内完成所有通道的信号处理任务。

因此,研究如何有效提升FPGA和DSP之间的数据传输速率以降低数据传输对DSP处理时间的占用,对实现多模多频GNSS接收机具有重要意义。

1 接收机硬件架构

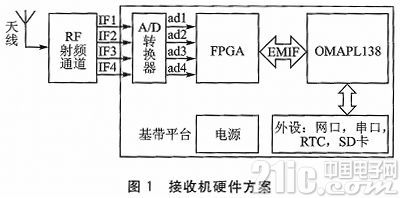

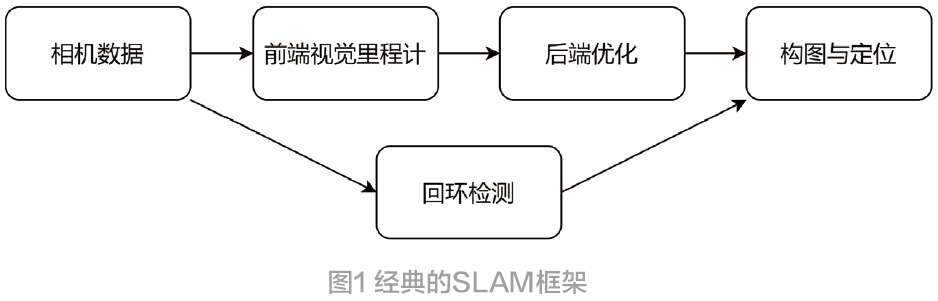

定制的基于FPGA+DSP架构的接收机硬件方案如图1所示。

接收机天线采用的是全频段天线,能够接收BDS、GPS、Galileo以及Glonass系统所有频点的卫星导航信号;射频通道RF完成导航信号的放大、下变频以及滤波等工作;基带平台中的A/D转换器对射频通道输出的中频信号进行采样,完成模拟信号到数字信号的转换;FPGA实现导航信号的捕获以及通道相关运算功能;DSP选用TI公司的OMAPL138,完成环路的更新以及定位解算功能。

2 数据传输分析

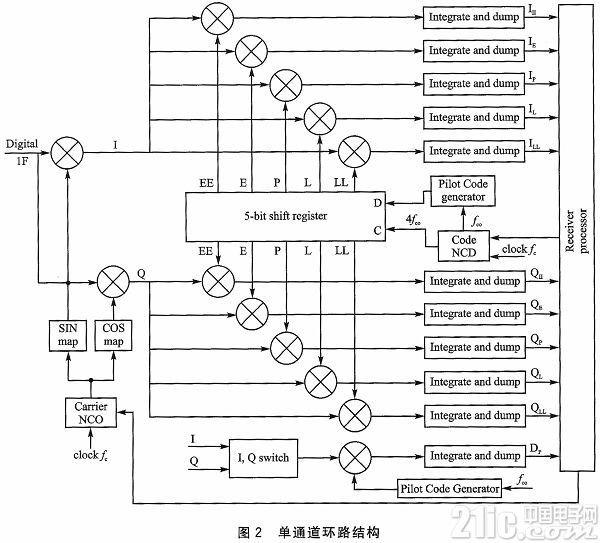

在接收的导航信号中,有些信号没有导频支路分量(如B1I、L1CA等),但是为了保证积分通道的通用性,FPGA内部积分通道均采用5路复相关器完成导频分量的跟踪,同时具有一路独立的相关器完成数据的解调功能。单通道内的环路结构如图2所示。

与传统的只有三路复相关器的接收机相比较,在图2所示的单通道内,增加了EE与LL两组复相关器、数据支路伪随机码发生器(data code generator)、数据解调器以及IQ切换单元(I,Q switch)。增加两路复相关器是为了能够实现性能良好的抗多径算法;由于在不同信号分量内数据支路与导频支路的相位关系不确定,因此需要在解调数据之前添加IQ切换功能单元。对于没有导频支路的导航信号,在接收机通道使用过程中无需使用IQ切换单元、数据解调相关器以及数据支路伪随机码发生器。

在通道更新之前,OMAPL138需要将FPGA内部完成的5组积分值读取到内部,完成相位延迟锁定环路(PLL)和伪码延迟锁定环路(DLL)的鉴相以及滤波,最后将环路更新的结果反馈至FPGA内部的相关通道中,从而完成一次环路的更新。在下面分析的过程中将误差计算、滤波以及PLL、DLL更新合称为“通道处理”。

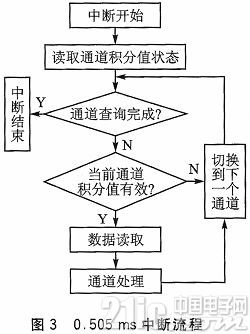

DSP执行0.505 ms中断任务的流程如图3所示。中断开始后首先读取所有通道相关积分标志,循环判断通道积分状态标志位,根据1ms相关积分状态标志位,进行相应通道处理。

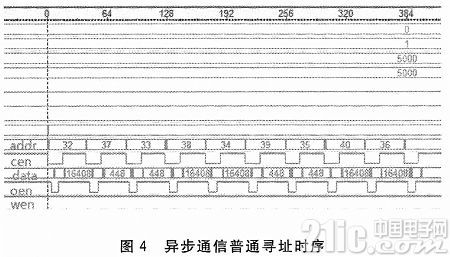

FPGA与OMAPL138之间通过EIMF总线进行数据传输。EIMF总线具有两种工作模式:同步和异步。程序设计初始阶段,接收机采用异步模式普通寻址方式进行数据传输。在分析数据传输时序的过程中,采用Altera逻辑分析仪软件signalTap对DSP与FPGA之间的异步通信时序进行仿真分析。分析结果如图4所示。

由图4中的片选信号cen可以看出,数据访问的时间由片选低电平以及两次访问数据间的高电平组成。其中,低电平时间主要由EMIF总线时序中的 setup、strobe以及hold时间构成;高电平代表读取数据的切换时间,视为无效时间,这段元效时间严重降低了数据传输速率。通过第一行的采样点以及采样频率可以估计出普通异步访问总线数据速率为3.0 03 MB。0.505 ms内跟踪通道数满足下式:

n·Ns/R+n·tsp+δt0.505 ms (1)

其中,R为EIMF通信速率(MB/s);Ns为单通道数据量(字节);tsp为单通道处理时间(s);δt为OMAPL138查询通道过程中的程序执行时间,在下面计算过程中忽略此时间。

在复相关器数为3(Ns=12字节),跟踪通道数n=12的传统接收机工作模式下,单通道处理时间tsp=4 μs;由式(1)可知,通道更新时间t=n·Ns/R+n·tsp+δt≈96μs,满足t 0.505 ms,因此OMAPL138能够完成12个通道的跟踪。但是在单通道内复相关器数量为5,同时具有一路解调数据相关器的情况下,单通道积分数据Ns增加至22字节,则跟踪通道数n44,不能满足项目中跟踪通道数为96的要求。

基于以上分析,下面将重点讨论如何通过缩短无效时间,以及通过数据读取与通道处理并行执行缩短数据传输占用DSP时间两方面来提高数据传输的效率。

3 数据传输优化方法分析与实现

3.1 消除数据读取间隔的无效时间

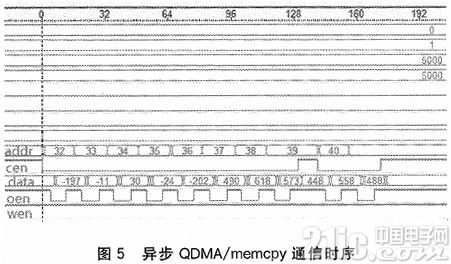

采用signalTap对memcpy或者QDMA数据通信进行仿真分析,分析结果表明两者在数据传输过程的时序关系一致,能够有效缩短数据访问时间。异步时序模式下QDMA/memcpy通信时序关系如图5所示。

由图5中的片选信号cen可以看出,在采用QDMA或者memcpy进行数据传输时,cen高电平仅出现一次,EMIF总线数据吞吐率提升至6.85 MB/s,缩短了数据传输占用OMAPL138的时间。由式(1)可以得出,跟踪通道数n70,不能满足设计指标,因此需要通过实现数据传输与通道处理的并行执行进一步缩短数据传输占用OMAPL138时间,实现在0.505 ms内完成96个跟踪通道的更新。

3.2 实现数据传输与通道处理并行执行

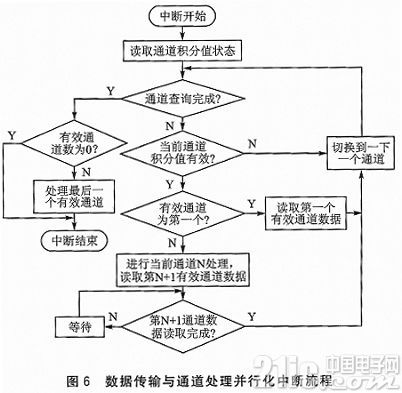

与memcpy方法进行数据传输相比较,QDMA数据传输方式能够通过修改软件算法方便地实现数据传输与通道处理并行执行,从而达到进一步缩短数据传输占用OMAPL138时间的目的。采用QDMA方式进行数据传输后的0.505 ms任务流程如图6所示。

图6与图3比较可以看出,在采用QDMA数据传输方式下,数据传输与通道处理任务执行算法得到优化,在查询到第一个通道积分值有效后,采用memcpy方式对该通道的积分数据进行读取,数据读取完成后开始查询下一个积分值有效通道,当查询到下一个有效通道后,将QDMA设置为开始读下一个通道数据;当通道处理完成后,检查QDMA是否完成通道数据的读取,如果完成则切换到下一个通道进行查询,若没有完成,则等待数据传输完成。当96个通道全部查询完成后,开始执行最后一个通道的处理任务,这保证了只有一个通道的积分值有效的情况下能够对这个通道进行处理;若96个通道的积分值均无效,则在查询完积分标志位后直接结束中断任务。

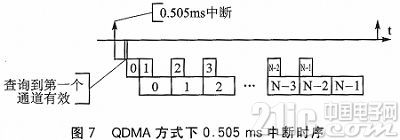

图7的0.505 ms中断内的任务时序图更直观地说明,采用QDMA方式数据传输有效缩短了数据传输占用OMAPL138的时间。传输步骤如下:查询通道状态;读取累积值标志位;通道数据读取;通道处理。

图7中的编号为有效通道的通道号,能够更加方便地看出在0.505 ms内,由于数据传输与通道处理的并行执行,将数据传输占用OMAPL138的时间缩减至一次数据读取的时间,从而完成数据传输的最优化。通道数量与数据传输速率的约束公式变为:

1·Ns/R+n·tsp+δt0.505 ms (2)

其中,R为OMAPL138与FPGA通信速率(6.85 MB/s);Ns为单通道数据量(22字节);tsp为单通道处理时间(4 μs);δt为OMAPL138查询通道过程中的程序执行时间。

结语

以工程实际为基础,在低功耗的前提下,针对如何有效提升FPGA和DSP之间的数据传输速率以降低数据传输对DSP处理时间的占用问题,通过在当前定制的卫星导航接收机硬件平台上对数据传输进行仿真分析,最终提出对数据传输采用QDMA方式进行优化,消除了连续数据读取间隔的无效时间,并实现了卫星信号处理与相关值数据传输的并行化,显著降低了数据传输对DSP处理时间的占用,使得在同样硬件平台上跟踪通道数由44个提高到96个,满足了项目设计的要求。本文的优化思想并不局限于设计实现基于DSP实现的GNSS接收机,同时为采用嵌入式MCU设计多通道GNSS接收机提供了理论依据。

评论