基于CPLD的数字光端机的设计

摘要:远程监控技术的应用随着日益发展的现代安防技术而变得越来越广泛。而由光纤作为传输介质的数字光端机,已经成为远程监控应用中的首选。本文详细介绍了数字光端机的架构与工作原理,完成基于CPLD的无压缩2路视频传输,2路音频传输和一路反向数据传输的数字光端机的设计。实验证明,系统工作性能稳定可靠,实时传输效果好,可广泛应用于安防行业。

本文引用地址:http://www.amcfsurvey.com/article/201610/308272.htm复杂可编程逻辑器件(CPLD)是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。它在现代数字通信系统中,其作用还是相当重要的。由于其编程灵活、设计开发周期短与先进的开发工具等特点使得对整个系统的设计调试周期大大缩短。而且对基带信号和整个系统的控制也能处理的很好。Altera公司推出的MAX II系列芯片EPM240T100C5

是一款性价比很高的CPLD芯片。共有240个逻辑单元,192个等效宏单元,内置8192bit的Flash,80个I/O口,低功耗,能满足大部分设计的需要。

数字光端机具有传输信号质量高,没有模拟调频、调相、调幅光端机多路信号同传时交调干扰严重、容易受环境干扰影响、传输质量低劣、长期工作稳定性差的缺点。它是将多路模拟基带的视频、音频、数据进行高分辨率数字化,形成高速数字流,然后将多路数字流进行复用,通过发射光端机进行发射,然后通过另一端的接收光端机进行接收,解复用,恢复成各路数字化信号,再通过数字模拟变换,恢复成模拟视频、音频、数据信号。本文实现了基于CPLD的无压缩2路视频传输,2路音频传输和一路反向数据传输的数字光端机设计。

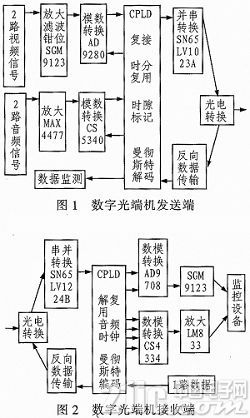

1 系统结构与工作原理

数字光端机的发射端工作原理:首先对视频图像信号(PAL/NTSC制式)和音频信号进行采集,转换为低速模拟信号。然后系统将2路无压缩视频信号和2路音频信号进行高分辨率的数字化,形成高速数字流,然后将多路数字流通过CPLD器件,运用Verilog HDL语言和时分复用的思想,实现正向数据的一次复接。最后将复接后的并行数据通过串化器转换为LVDS(低压差分信号),形成高速差分信号后,通过光电一体模块进行发送。如果正常发送,则将通道信号灯点亮,否则,说明传输不正常。以及接收传输过来的数据信号,进行曼彻斯特解码操作后,发送到相应的接收器件上,观察结果。

数字光端机的接收端工作原理:首先进行数据的接收。然后按照时分复用的发送规则解复用,分别得到各自的数据。最后再经过数模转换,电平转换恢复成模拟视频,音频信号。发送到各自相应的器件上,观察结果。如果能正常接收及转换,则将相应通道信号灯点亮,否则,说明输出不正常。以及将一路数据信号进行曼彻斯特编码,并发送到光电一体模块上进行发送。

2 系统模块设计与实现

数字光端机包括以下几个模块:视频模块、音频模块、数据模块、并串/串并转换模块、光电一体模块等。

2.1 视频模块

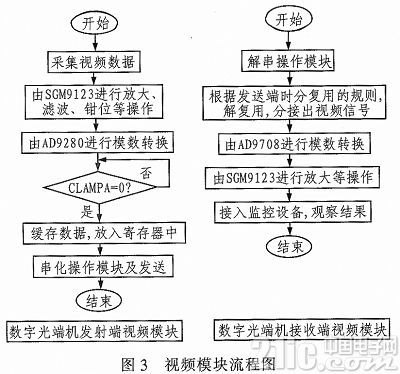

数字光端机发射端视频模块实现的功能是将摄像头采集到的低速模拟信号进行放大、滤波、钳位、并模数转换,为CPLD提供可用于一次复接的数字信号。数字光端机接收端

视频模块实现的功能是将CPLD二次解复用的数字信号进行数模转换,转换为模拟信号后再进行放大,发送到监控设备上。

模数转换部分采用ANALOG DEVICES公司的A/D转换芯片AD9280。它是一个单电源供电,8-bit,32MSPS采样速率的单片集成电路。并是集采样、保持、放大和电压参考于一体的模数转换器。内置钳位功能,但由于SGM9123具有钳位功能,则AD9280的Clamp引脚接地。由SGM9123输入的模拟视频信号所产生的8位并行数据,不经过编码和压缩等处理,直接送入CPLD芯片进行时分复用处理。

数模转换部分采用ANALOG DEVICES公司的D/A转换芯片AD9708。它的采样速率高达125MSPS,是8位并行数据输入,差分电流输出,高输出阻抗的数模转换器。将经过D/A转换后产生的差分电流,进行缓冲放大等操作后,即可送入监控设备查看结果。这里进行的放大等操作所使用的芯片还是SGM9123。详细操作,请参照上述说明。视频模块总体设计,可参考图3。

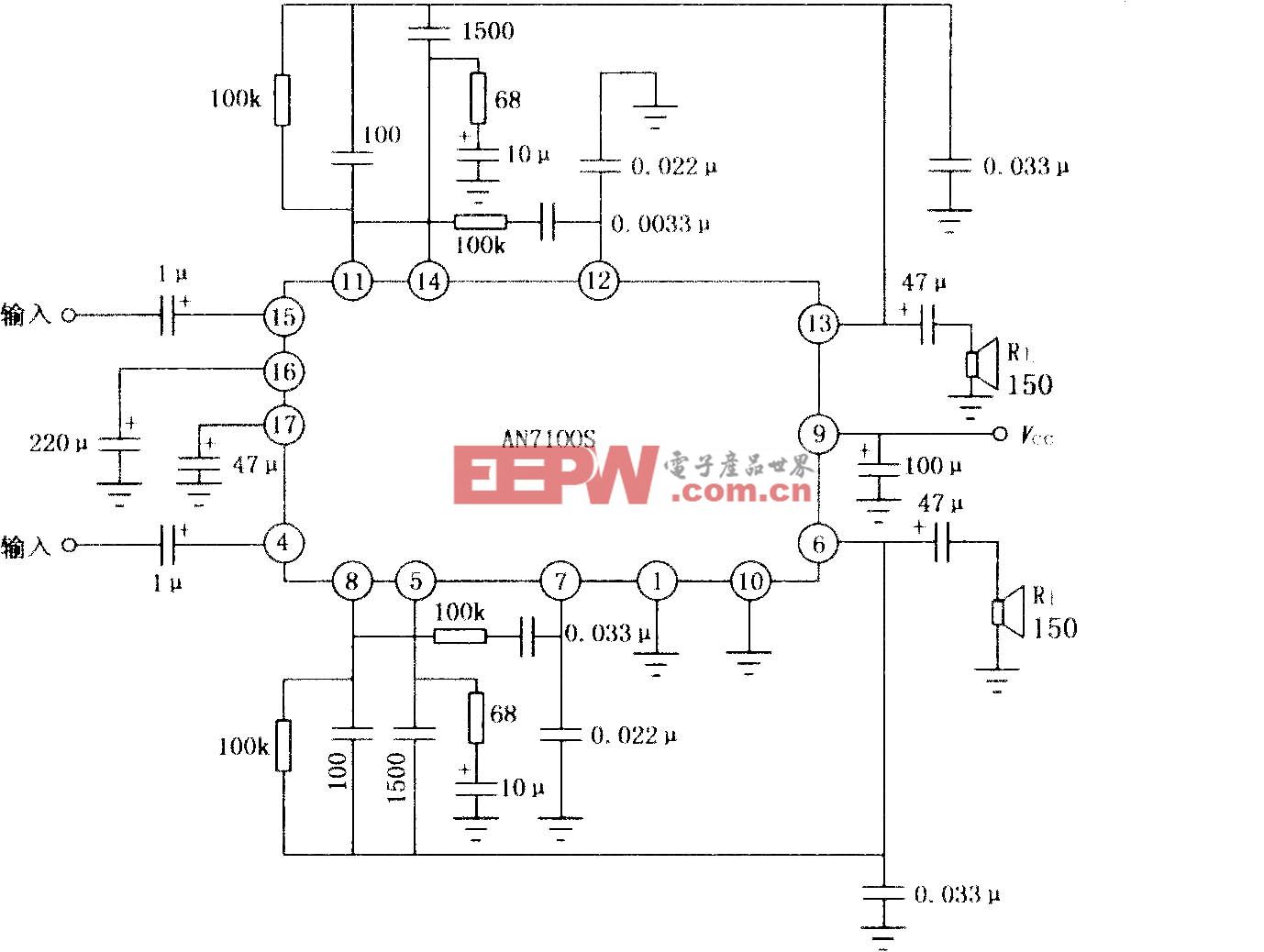

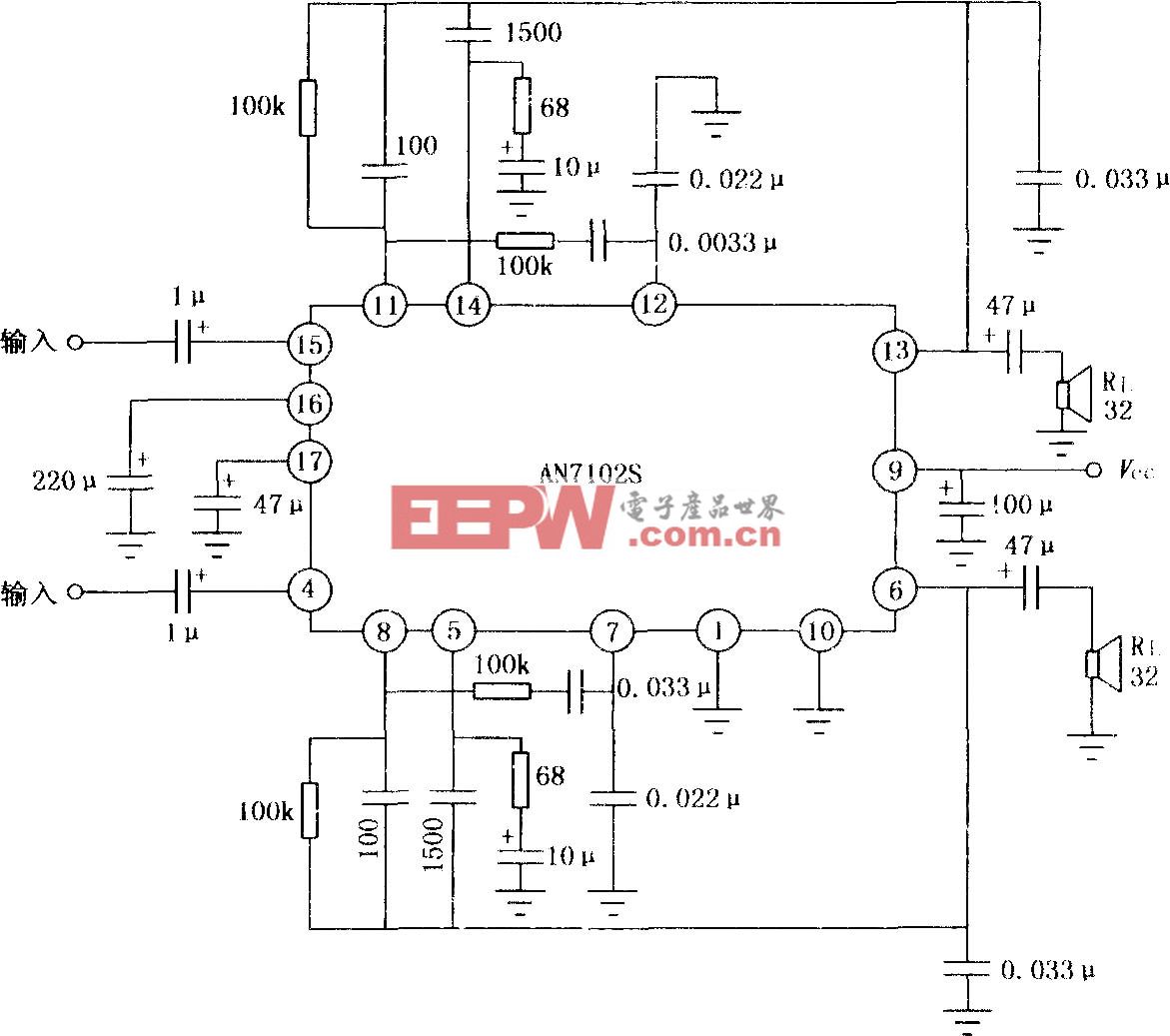

2.2 音频模块

音频模块使用的是运算放大器芯片MAX4477。它是具有宽频带,低噪声,低失真,轨对轨输出,和支持单电源供电(2.7~5 V)等特性的运算放大器。

模数转换部分采用的是音频A/D转换芯片CS5340。它是一个5阶多位Delta—Sigma调制器,3.3~5 V电压供电,支持取样频率从32~192 kHz,是24位双通道立体声ADC。

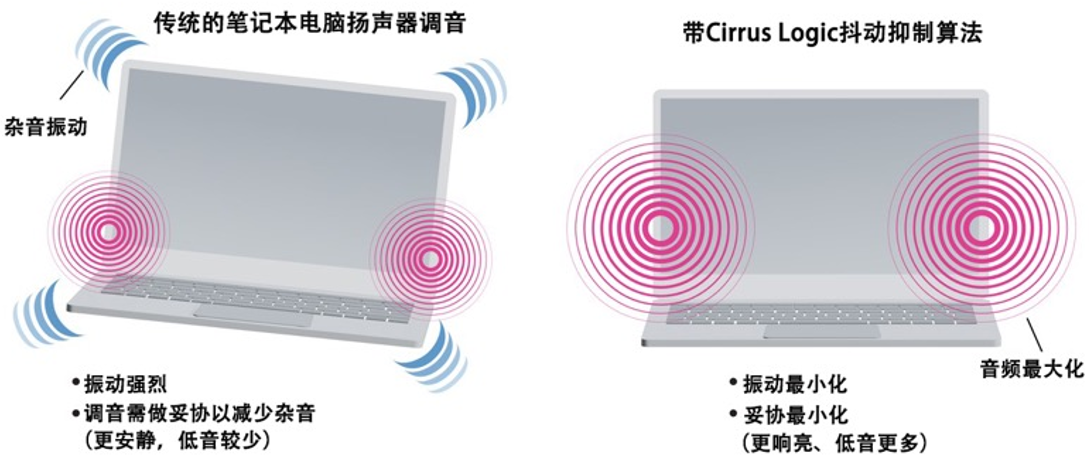

数模转换部分采用Cirrus Logic公司的音频D/A转换芯片CS4334。它是完整的立体声DAC系统,包含插值,1-bit D/A转换和输出模拟滤波。它具有5 V单电源供电,片上数字去加重,24位转换和支持所用主流音频数据接口格式的特性。

放大模块部分采用双音频运算放大器芯片LM833。它具有低噪声,高速和宽频带等特性。它放大传输过来的模拟音频信号,并输送到相应的设备中,并观察结果。

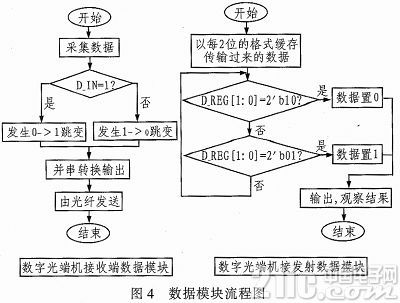

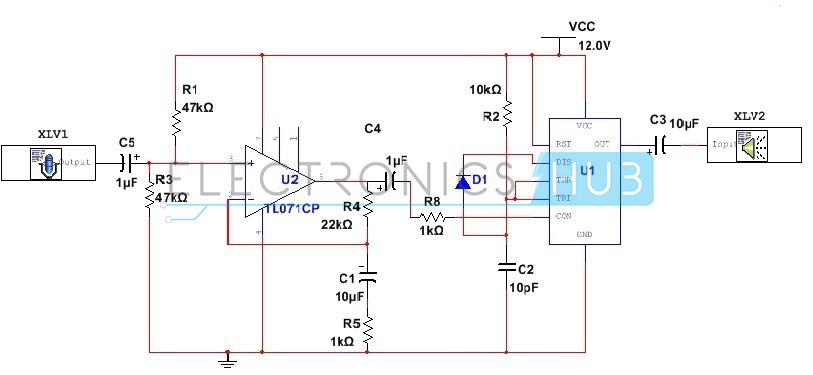

2.3 数据模块

本设计的发射端和接收端都采用的是德州仪器(TI)公司推出的RS-485数据总线半双工收发器件SN65HVD3082E。它具有5 V电源供电,符合TIA/EIA-485A标准,传输速率最高位200 Kbps,低静态功耗,总线引脚ESD(静电释放)保护高达15 kV等特点。数据模块的设计,其流程图为图4所示。

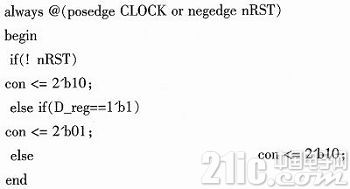

由于该路数据的最高传输速率仅为200 kb/s,而光纤本身是类似带通的通道,不像双绞线或低通信道,所以直接传输低速率的数据信号会造成很多误码,是不可取的,所以本设计采用了曼彻斯特编解码技术。它是将时钟和数据包含在数据流中,在传输代码信息的同时,也将时钟同步信号一起传输到对方,每位编码中有一跳变,不存在直流分量,因此具有自同步能力和良好的抗干扰性能,适合光纤传输。曼彻斯特编码实现,可参考以下代码:

其仿真结果为图5所示。

2.4 并串/串并模块

数字光端机发射端串化模块实现的功能是,在经过视频和音频信号进行一次复用后,输出10位并行数据。必须再经过串化操作,将10位并行数据通过高分辨率的数字化形成高速数字流,输入到光电一体模块进行电光转换后,再通过光纤进行传输。数字光端机接收端解串模块实现的功能是,首先对传输过来的高速差分信号,进行解串操作,即一次分接。之后,变成CPLD可识别的低速数字信号。然后再根据发射端时分复用的规则来解复用,即二次分接。之后,分离出视频、音频信号,并将其传送到相应的监控设备上。

串化器能将输入的10位并行数据转换为具有内嵌时钟的高速差分数据流,再通过光电一体模块转换为光信号并通过光纤发送到对端。解串器在与串化器同步后,能重建并行时钟,并将并串转换后的数据传送给CPLD芯片进行处理。如果是处于随机锁定同步模式下,解串器还能工作在Open—Loop应用下和有能力支持带电热插拔。光端机接收端对数据分接部分的处理,可参考以下代码:

2.5 光电一体模块

本模块主要实现的功能是,在发射端完成对信号的串化操作后,将高速数字差分信号转换为光信号,并通过光纤发送到对端。而接收端是,接收来自光纤传输过来的信号,将其转换为数字信号,以便进行解串操作等进一步处理。本设计采用的是1.25G/84 M 1X9 Transceiver,单模单纤双向光电收发一体模块。它可以通过单纤实现双向传输,1.25G为视频、音频信号传输,84 M为反向数据传输。通过33 V/5 V供电,传输波长为1310/1550。

3 测试分析

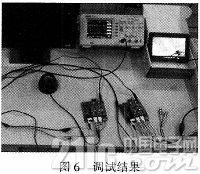

本次设计,首先测试了各个模块是否能正常工作。包含音视频数据和反向数据是否能正常传输,发送是否稳定,发送频率是否符合要求等方面。经测试分析后,视频带宽为

8 MHz;反向数据传输速率最高可达到200 kbps;传输距离最高可达20 km,1.25G/84 M的传输速率;满足设计需求。最后显示的结果如图6所示,证明数据能正常发送且稳定,图像清晰。

4 结束语

本次远程监控系统的设计与研制,实现了各个监控点和总监控室的信号远程传输。保证了信号实时传输、稳定显示以及画面声音质量清晰等功能。还能将各个监控点采集到的视频和音频信号通过采集卡存储下来。该设备简单,成本低,便于维护且抗干扰能力强,因此本系统具有较好的实验效果和市场应用价值。

评论