SOC设计流程及其集成开发环境

片上系统(SOC——SystemOnaChip)是指在单芯片上集成微电子应用产品所需的全部功能系统,其是以超深亚微米(VDSMVery Deep Subnicron)工艺和知识产权(IP——Intellectual Property)核复用(Reuse)技术为支撑。

SOC技术是当前大规模集成电路(VLSI)的发展趋势,也是世纪集成电路技术的主流,其为集成电路产业和集成电路应用技术提供了前所未有的广阔市场和难得的发展机遇。SOC为微电子应用产品研究、开发和生产提供了新型的优秀的技术方法和工具,也是解决电子产品开发中的及时上市(TTM——Time to Market)的主要技术与方法。

片上系统(SOC)引入导致嵌入式系统的设计方法变革

就目前现状而言,若以嵌入式系统所采用的核心器件——处理器进行划分,嵌入式系统可以分为三种类型:基于微控制器(MCU)的嵌入式系统、基于信号处理器(DSP)的嵌入式系统、基于微处理器(MPU)的嵌入式系统。其中基于MCU的嵌入式系统是一种低端嵌入式系统,这种系统共同的特点是系统运行速度低、数据处理能力弱和存储空间有限(K级),因此只适合于低端的电子产品;基于DSP的嵌入式系统是中低端嵌入式系统,这种系统共同特点是系统运行速度较高、数据处理能力强,但是存储空间也是有限的(K级M级);基于MPU的嵌入式系统通常可以分为两种类型:基于CISC架构微处理器的嵌入式系统和基于RISC架构微处理器的嵌入式系统。

其中,CISC架构微处理器通常是由x体系结构进行嵌入应用扩展而获得一种类型的嵌入式处理器;RISC架构嵌入式微处理器可以分为三大体系结构:arm体系结构、PowerPC体系结构和MIPS体系结构。基于这三大体系结构的嵌入式处理器品种繁多,功能也各异。但基于此类处理器的嵌入式系统共同特点是运行速度高、数据处理能力强、存储空间足够大(G级),因此是一种高端的嵌入式系统。

无论是低端、中端或高端嵌入式系统,其经典的设计方法仍然是一种板级电子系统设计方法:首先,根据嵌入式系统的设计要求,并且按一定的设计规则,把整个嵌入系统划分成具有特定功能的若干个功能模块,如处理器模块、信号采集模块、执行机构控制模块等;然后,根据系统模块划分的结果,选择现成已商品化的模块或自行研制各功能模块;最后,把这些模块组合成一个完整的嵌入式系统。随着集成电路技术的发展和嵌入式系统小型化和微型化等方面要求,板级电子系统设计已经开始出现如下几个方面的变化:

(1)嵌入式系统的核心器件——处理器(包括MCUDSP和MPU等)已经开始向单芯片系统方向发展。例如经典8051系列微控制器已经从原来只有简单的并行I/O和串行接口(UART)发展到具有并行I/O、多UART接口、红外线传输、A/D转换器、D/A转换器、模拟比较器、可编程模拟信号放大器、滤波器、PWM等的可编程片上系统(SOPC)型MCU芯片,即只需要极其少量的外围器件就可以完成一个具有特定功能的嵌入式系统的设计工作;

(2)嵌入式系统的核心器件——处理器(包括MCUDSP和MPU等)已经开始向平台级芯片方向发展,目前所推出的高档嵌入式处理器,无论是基于arm体系结构、PowerPC体系结构还是基于MIPS体系结构的高档嵌入式处理器,在单芯片上不仅具有各种功能的外围接口,而且通常内置有RISC协处理器(例如RISC微控制器数字信号处理器等),同时还具有测试和自开发接口,因此完全可以把其认为是一种硬件平台级芯片,这样使得嵌入式系统设计与开发重点由板级系统设计转到芯片级系统设计;

(3)嵌入式系统的核心器件——处理器(包括MCUDSP和MPU等)已经向高处理速度方向发展,从而使板级电子系统的PCB设计难度增加,设计重点不仅是PCB版图设计,更重要的是电磁兼容性和系统可靠性设计。由此可见,由于嵌入式系统的核心部件——处理器向片上系统(SOC)发展板级设计工作量逐渐减少,未来的嵌入系统的发展的重点将从板级电子系统设计转到芯片级电子系统设计上(即转移到片上系统设计上)。因此,基于片上系统(SOC)设计方法必将成为未来嵌入式系统的发展主流;

对于一般的嵌入式系统设计者来讲,尤其是国内的嵌人式系统设计者来讲,基于片上系统(SOC)的设计方法还是主要停留在板级电子系统设计方法层次,即利用已经推出的商用SOC芯片进行板级电子系统设计。这主要是由于设计工具资金集成电路工艺等方面的限制所致,但是由于近年来多晶圆(MPW)项目和CPLD/FPGA技术的发展,尤其是可编程片上系统(SOPC——SystemonaProgrammablechip)芯片的出现使得一般的系统设计者进入芯片级电子系统设计成为可能。自从1999年出现第一个可编程片上系统(SOPC)器件以来,已经有众多可编程器件供应商推出了具有自己特色的可编程器件,最为典型的是世界上两大可编程器件供应商——Xilinx公司和Altera公司在FPGA/CPLD基础推出的系列可编程片上系统器件。其中Xilinx公司先后推出的可编程片上系统器件有Virtex系列VirtexE系列、VirtexII系列、VirtexPro系列、Spaxtan系列、SpartanII系列等;Altera公司先后推出的可编程片上系统器件有APEX系统、APEX II系列、Mercury系列、Excalibur系列、Stratix系列、Cyclone系列等。每个系列器件都有多种产品,以适用于不同的应用要求。因此,对于国内一般的系统设计者来讲,基于可编程片上系统(SOPC)器件的嵌入式系统设计将是进入芯片级电子系统设计的敲门砖。

那么,从板级电子系统设计到芯片级电子系统设计转变将导致哪些方面的变化?主要表现在如下几个方面:

(1)在设计描述工具方面,传统的板级电子系统设计主要采用电路原理图和元器件外形封装图作为设计描述语言工具而现在的芯片级电子系统设计主要采用文本方式的硬件描述语言(HDL——Hardware Description Language)作为设计描述语言工具

(2)在设计流程方面板极电子系统设计主要经历电子系统原理图设计与仿真、印刷电路板(PCB)设计与仿真分板(包括信号完整性分析、电磁兼容性分析等)等二个阶段,而芯片级电子系统设计通常需要经历系统级设计与仿真、算法级设计与仿真、寄存器传输级(RTL)设计与仿真、逻辑综合与验证、版图设计综合与验证等个阶段;

(3)在软硬件协同设计方面,板级电子系统设计所采用的方法是先进行硬件系统设计后再进行软件系统设计的方法,难以实现软硬同步设计或协同设计,而芯片级电子系统设计可以比较容易实现软硬件同时设计或协同设计;

(4)在设计实现方面,板级电子系统设计主要基于具有特定功能的集成电路器件,而芯片级电子系统设计主要是基于具有特定功能的电路模块——知识产权核(IP核)。因此,板级电子系统设计与芯片级电子系统设计无论是在设计方法上还是在设计工具方面都发生了较大的变化。

随着现代信息技术的发展,电子产品生命周期越来越短,特别是电子工业技术不断发展,基于深亚微米和超深亚微米的超大规模集成电路技术的片上系统(SOC)芯片需求日益扩大,传统的板级电子系统设计方法已不能适应产业界对电子产品需求。因此,基于知识产权(IP)核复用的芯片级电子系统设计方法将成为嵌入式系统设计的主流方式。

基于可编程片上系统(SoPC)的设计流程

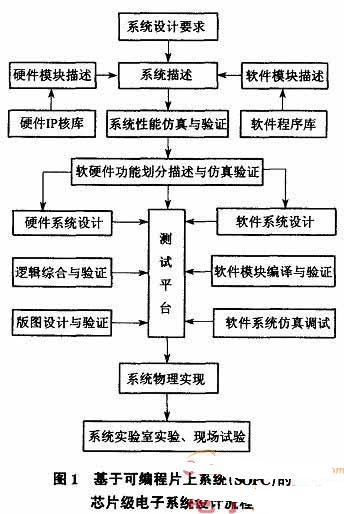

基于可编程片上系统(SOPC)的芯片级电子系统设计主要有两大支撑点:可编程片上系统器件所能提供的片上资源和可复用IP核库所能提供的IP核资源。其中可编程片上系统器件所能提供的片上资源是由集成电路工艺技术发展决定的,对于系统设计者来讲,应根据设计要求尽量选择合适的器件;可复用TP核库所能提供的IP核资源需要通过系统设计者自行建设。在基于SOC的电子系统设计中,针对各类专门技术、专门应用、专门工具、专门生产工艺、专门产品的IP资源库的建设和共享已形成一种规范,贯穿在系统设计的全过程。图1为典型的基于IP核库的片上系统(SOC)设计流程:

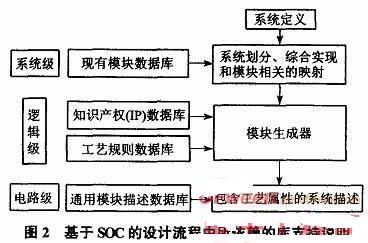

从图1可以看出,在基于可编程上系统(SOPC)的嵌入式系统设计流程中,除了需要强有力的EDA设计工具支持外,离开充分的资源库的支持,可以说是寸步难行,并且必将失去竞争力。从总体上讲,各个层次的IP库和EDA工具是芯片级电子系统设计者必备的两翼,可选的IP核库资源是一种设计者能力的表征。图2为芯片级电子系统设计中自顶向下设计方法的流程中所依赖的库支持说明。

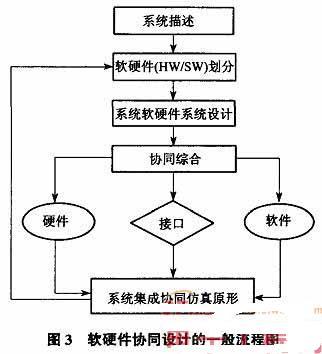

在图1的片上系统(SOC)设计流程中,除了需要强有力的IP核库和EDA工具支持外,与传统的专用集成电路(ASIC)设计流程最明显的区别就是——软硬件协同设计,图3给出软硬件协同设计的一般流程。

在软硬件协同设计的过程中,传统的硬件描述语言(VHDL、Verilog HDL)和软件设计语言(C/C++)是无法适应软硬件协同设计这一种新的设计方法上的突破,为此必须使用新的系统级描述语言——S 3.基于可编程片上系统(SOPC)的集成设计环境片上系统(SOC)设计所需要的EDA工具,若从硬件设计角度看,在设计流程的前端与ASIC设计差别不大。但是,从整个芯片设计角度出发,这两种类型的芯片设计区别较大。这是因为,在SOC设计中,一般都含有微处理器,所设计的系统级芯片都必须有设备驱动程序与操作系统或嵌入式实时操作系统接口,必须有应用程序完成数字计算、信号处理变换、控制决策等功能。因此,在设计的前期需要进行软硬件协同设计,以便确定那些功能是由硬件完成的,那些功能是由软件完成的,并且进行适当划分。在设计的中后期,要进行软硬件协同验证,即把软硬件设计放到一个虚拟的集成环境中进行仿真验证,以便验证硬件的性能是否达到设计目标,软件功能是否实现设计要求。

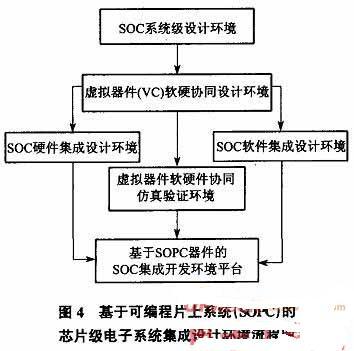

根据可编程片上系统(SOPC)设计流程和软硬件协同设计的一般流程作者提出基于可编程片上系统(SOPC)的芯片级电子系统的集成设计环境如图所示此集成环境是一种典型的软硬协同设计集成环境(或平台)是由二个不同层次不同功能的EDA集成设计环境组成

第一层次的EDA集成设计环境是SOC系统级集成设计环境主要用于完成嵌入式系统的系统级设计首先需要根据客户的要求进行系统的功能定义和性能评估以便确定系统规格其次根据已经确定的系统规格应用系统级描述语言(C/C++或System C等)进行系统设计描述与设计验证以便确定所定义的系统规格在功能上是否可以实现再次在证明了系统规格在功能上可以实现后就需要进行系统软硬件功能划分以便确定系统的哪些功能是由软件系统完成的哪些功能是由硬件系统完成的哪些功能需要软硬件协同完成对于既可以通过软件系统完成也可以通过硬件系统完成的功能需要进行性能与成本的评估最后对已经确定的硬件系统功能还需要进行芯片与PCB功能的划分以便确定哪些功能可以在芯片上实现哪些功能只能在PCB上实现

第二层次的EDA集成设计环境是SOC硬件系统集成设计环境和SOC软件系统集成设计环境主要用于完成嵌入式系统的软硬系统设计首先根据系统级设计中的功能划分分别进行SOC的硬件系统设计和SOC的软件系统设计此时的硬件系统设计和软件系统的设计是并行进行的在硬件系统设计中通常经历几个设计阶段行为描述与验证(包括硬件系统的系统级算法级寄存器传输级的行为描述与仿真验证)逻辑综合与验证可测性设计综合与逻辑生成器件适配与仿真验证器件物理编程与物理验证版图生成与验证其中前个设计阶段是基于SOPC的硬件系统设计流程在软件系统设计中通常经历如下几个阶段软件系统编辑软件系统编译软件系统仿真调试软件系统编程等其次在软硬件系统设计过程中为了确保系统的性能价格比达到最优需要不断进行软硬件协同设计通常在硬件系统行为描述与仿真之后就可以把所设计的硬件系统与软件系统置于虚拟器件的软硬件协同仿真验证环境中以便验证硬件系统集成的系统所能达到的功能性能成本等从而使得所实现的芯片级电子系统的性能价格比达到最优

综上所述基于可编程片上系统(SOPC)的嵌入式系统集成设计环境是一个相当复杂的集成EDA开发环境常见的可编程片上系统集成化EDA开发套件——Altera公司的Quartus II系列的EDA工具套件和Xilinx公司的ISE.x系列的EDA工具套件的储存成化程度虽然较高但也难以达到图所示的集成化程度因此需要系统设计设计者根据现有的商用化EDA工具构建这样的集成设计环境有理由相信在不久的将来将会推出类似的集成EDA工具环境

片上系统(SOC)是嵌入式系统发展方向

嵌入式系统的核心部件是微处理器由于集成电路技术的发展以及电子产品及时面市的要求促使微处理器(包括微控制器数字信号处理器嵌入式处理器)向单芯片系统方向发展从而使得基于片上系统(SOC)的电子系统成为嵌入式系统的发展方向和主流目前国内的基于片上系统(SOC)的嵌入式系统设计大都停留在板级电子系统设计水平随着可编程片上系统(SOPC)器件的应用发展相信在今后的若干年内基于SOC的嵌入式系统设计会逐渐过渡到芯片级电子系统的设计水平由于芯片级电子系统设计方法与板级电子系统设计方法有着本质的区别因此了解与掌握芯片级电子系统的设计流程集成设计环境对于系统设计者来讲是至关重要的为此本文以图示方式直观地给出基于可编程片上系统(SOPC)的芯片级电子系统设计流程和集成设计环境全面展示了芯片级电子系统所涉及到的问题ystem C(或其他类似语言)才能完成

软硬件协同设计通常是从一个给定的系统任务开始的通过有效地分析系统任务和所需要的资源采用一系列的变换方法并且遵循特定的准则自动生成符合系统功能要求的符合实现代价约束的硬件和软件框架这种全新的软硬件协同设计思想需要解决许多问题系统级建模系统级描述语言软硬件划分性能评估协调综合协同仿真和协同、验证。

评论