利用FPGA实现外设通信接口之: 典型实例-VGA接口的设计与实现

10.9典型实例19:VGA接口的设计与实现

10.9.1实例内容及目标

1.实例的主要内容

本节旨在设计实现了FPGA与VGA显示器的接口,帮助读者进一步了解VGA接口的时序和设计方法。

本文引用地址:http://www.amcfsurvey.com/article/201706/348801.htm2.实例目标

通过本实例,读者应达到以下目标。

·掌握VGA接口的标准时序。

·掌握利用FPGA设计驱动的基本思想和方法。

·熟练掌握状态机的使用。

10.9.2VGA接口实例内容

红色飓风开发板的VGA接口可以产生8种颜色,可以用来显示字符和简单图形。本实例要求通过VGA接口,在显示器上依次显示8种颜色的彩色条纹,条纹宽度相同。

10.9.3FPGA代码设计实现

按照VGA时序要求产生行/列同步信号,并且在指定的时间(有效像素期间)将要显示的颜色数据输出到RGB。

不同的显示模式和刷新频率下,具体同步信号前、后、同步信号、有效像素数是不同的,要根据像素时钟频率来设置。以800×600,60Hz为例,像素时钟为40MHz,即:

像素时钟=(800+40+128+88)×(600+1+4+23)×60=40MHz

设计中可根据系统时钟频率来选择合适的显示模式。

10.9.4ModelSim仿真验证

1.行显示

设定一个列计数器,计数到相应的值时,给出相应的同步信号,并在像素有效期间,输出有效的颜色数据,行计数器通过检测列同步信号来计数,检测到列同步信号,表示新一行的开始,这样就可控制在不同的行显示不同的内容。

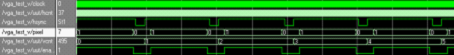

仿真结果如图10.45所示。

图10.45行显示仿真结果

其中,hcnt为列计数,列计数到有效像素时,给出enable信号,只有enable信号为高时,才给出有效像素数据,并且在每个同步信号后,行计数器加1。

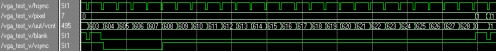

如图10.46所示为行同步信号产生时仿真结果,当计数到604-1=603行时,给出行同步信号,同步信号低电平持续4个行的时间,同步信号后持续21行的时间,之后再从第一行第一列开始。

图10.46行同步信号产生后仿真结果

2.列显示

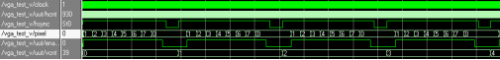

如图10.47是列显仿真结果。列显示和行显示不同在于,同一行的像素,计数到不同的值时,输出不同的颜色数据,每一行都是如此,最终就可得到列显的彩色条纹。

图10.47列显仿真结果

10.9.5小结

本节对利用FPGA来驱动VGA接口显示器的方法做了介绍,并通过编译下载在红色飓风的开发板上实现

评论