高云半导体推出I3C高速串行接口解决方案

山东济南,2018年1月9日讯,山东高云半导体科技有限公司(以下简称“山东高云半导体”)今天宣布推出基于低密度小蜜蜂Ⓡ家族的GW1N-9 FPGA芯片的SDR-模式I3C IP (Master-Slave-Combined )高速串行接口解决方案,包括相关IP软核、参考设计及开发板等完整解决方案。

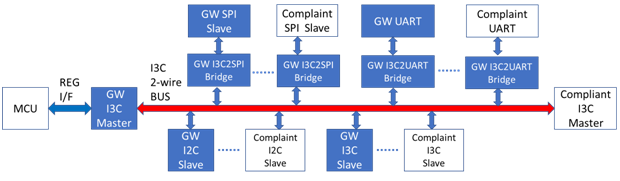

本文引用地址:http://www.amcfsurvey.com/article/201801/374142.htmI3C是MIPI联盟一个新的通讯协议,该协议兼容并扩展了传统I2C通讯协议,其总线为两线式串行总线。高云I3C IP遵循MIPI联盟I3C总线的通讯协议,集I3C Master和Slave于一体,是一个参数可配置、基于高云半导体FPGA芯片的IP设计。该IP可动态地配置成I3C Master或 Slave,实现I3C Master与I3C Slave或I2C Slave的通信,从而完成I3C通讯协议的各种功能。高云I3C Master与 Slave IP及高云I2C Slave IP可与遵循MIPI联盟I3C通讯协议的其他Master或Slave外设,以及遵循MIPI联盟I2C通讯协议的其他Slave外设直接相连通讯。

高云半导体软核研发部门负责人高级经理高彤军先生强调:“高云开发I3C IP核分两步走,目前的初级版支持单倍数据速率(SDR)模式,后续升级版会支持双倍数据速率(DDR)模式,进一步提高数据传输速率至33Mbps或以上。此外,今天发布的高云I3CIP,具有兼容并扩展I2C协议的功能,可直接与I2C Slave接入通信;后续升级版还附带配套设计的I3C至SPI链接桥和I3C至UART链接桥。今后连带发布的高云I3C-ECO-IP群组,将包括I3C2SPI-bridge、I3C2UART-bridge、SPI-Master-Slave-Combined IP、UART IP,从而能使I3C Master通过该链接桥直接与传统的SPI和UART 接入通信。这为方便业界迅速运用I3C技术提升其电子产品设计的速度与效能,并兼具维系支持传统外设,实现新老结合,降低成本,持续创新的最大性价比、性效比产品策略,铺平了道路。”

高云半导体总裁兼CTO宋宁博士表示:“高云I3C IP及其FPGA设计具有低引线数、可扩展性、低功耗、更高的容量等创新性能,能有效的减少集成电路芯片系统的物理端口、支持低功耗、高数据速率和其他已有端口协议的优点,为支持现代移动手持设备、智能驾驶、IOT设计添加了许多增强的特性。”

I3C应用举例

l力学感知(陀螺仪、加速计等)

l环境感知(声、光、温度、湿度等)

l仿生学感知(指纹、心率、呼吸等)

l通讯(近场通讯、远红外通讯等)

GW I3C基本特性

l高度灵活的参数可调设计,允许用户精确调整数据/时钟信号的周期,从而实现宽范围的数据发送速度调节。

l支持静态地址通讯

l支持动态地址机制

l支持I3C地址仲裁

lSingle Data Rate(SDR)

l支持I2C (Slave Only)消息

GW I3C高级特性

l支持热接入(Hot-Socket)

l支持热接入时动态地址分配

l支持Slave请求Secondary Master(SDR-Only)

l支持线载中断(In-band Interrupts)

l支持CCC’s (Common Command Codes) 命令

GW I3C传输速度

高云半导体云源软件支持GW I3C(Master-Slave-Combined )IP的全流程自动设计。GW I3CSDR模式最高数据传输速率达到12.5Mbps。

GW1N-9 FPGA

GW1N-9芯片为I3C协议专门设计可动态切换模式的IO电路,具有这一新特性的IO安排在芯片的上下两个Bank上。用户在使用这些IO时软件模型无需改变,只需在约束文件中将I3C Mode打开即可。

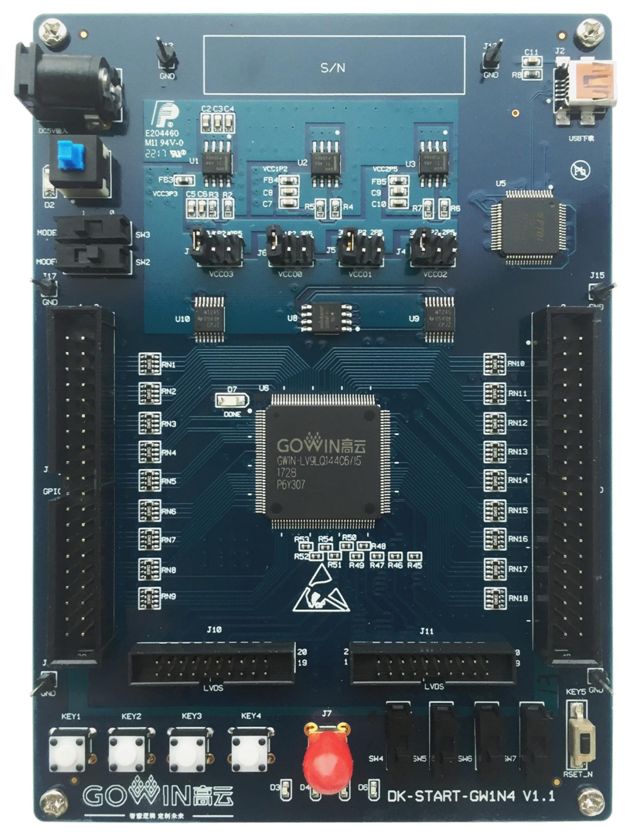

GW I3C IP开发板与参考设计

高云半导体提供通过实测验证的I3C IP开发板,已配置好相关电路,可将多块开发板连接在一起进行I3C BUS通讯实验。

评论