一种新型共模反馈结构

作者 胡国林 电子科技大学(四川 成都 610054)

本文引用地址:http://www.amcfsurvey.com/article/201807/389580.htm胡国林(1991-),男,硕士,工程师,研究方向:集成电路。

摘要:提出并设计了一种应用于CMOS全差分运放结构中的共模反馈电路。同传统结构的共模反馈结构相比,该结构能够使输出共模电平具有零延迟建立的特性,同时,不影响全差分运算放大器的输出摆幅,并且相较于传统结构,减少了开关数量,降低了开关电荷注入、时钟馈通,消除了初始电荷的影响。此新型共模反馈结构既有连续时间共模反馈速度较快、精度较高的优点,又有开关电容共模反馈输出摆幅大线性度好的优点。基于 Cadence spectre 对电路进行了仿真验证,结果表明,该结构的共模反馈具有快速的建立时间以及较大的输出摆幅。

0 引言

差分放大器是最重要的电路发明之一,它可以追溯到真空管时代。由于差分放大具有很多有用的特性,所以它已经成为当代高性能模拟电路和混合信号电路的主要选择。而带有共模反馈结构的全差分运算放大器是普遍运用的基本电路单元,广泛应用于各种模拟器件中,如A/D,D/A等[1-2]。

具有高输出摆幅、快速稳定和高精度的全差分运算放大器对模拟电路的设计尤为重要,而共模反馈结构直接影响到全差分运算放大器的各项性能,已有许多文章对某些性能提出了改进的结构[3-5]。共模反馈结构可以分为连续时间共模反馈结构和开关电容共模反馈结构。连续时间共模反馈结构主要应用于连续时间电路中,但是在连续时间共模反馈结构中如果通过电阻检测输出共模电压会显著降低电路的差动电压增益,通过MOSFETs作为检测器件会限制全差分运放的输出线性范围。开关电容共模反馈结构在这几方面具有优势[6],但传统开关共模反馈结构的共模电压建立时间较慢,共模稳定电压波动较大,且因使用较多MOS开关而通过时钟馈通和电荷注入引入噪声,限制了全差分运算放大器的速度和精度。

1 传统共模反馈结构分析

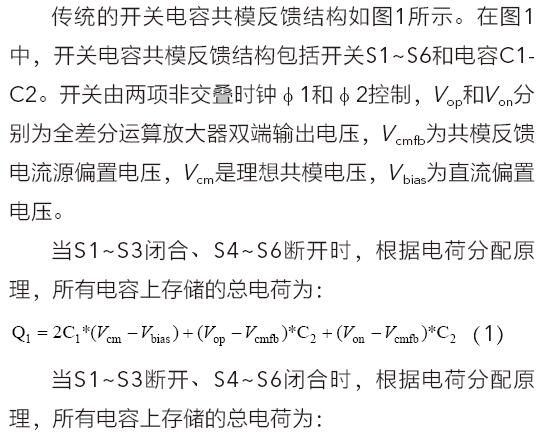

1.1 传统开关电容共模反馈结构

由式(3)可知,开关电容共模反馈首先检测输出共模电压,再与理想共模电压比较,最后叠加一个直流偏置电压来调节共模反馈电流源偏置电压Vcmfb,这需要一个比较长的建立时间,并且开关数量较多,电荷注入和时钟馈通的影响较大。

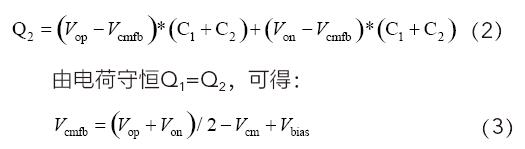

1.2 传统连续时间共模反馈结构

传统的连续时间共模反馈有多种结构,其中一种低功耗结构如图2所示。这里,M1~M4都是匹配的,源耦合对M1-M2和M3-M4一起检测共模输出电压并产生一个与输出共模和Vcm的差成比例的输出电压Vbias。

此结构能正常工作的前提是M1~M4总工作在放大区且电压Vop-Vcm和Von-Vcm能看成是小信号输入。即使这些电压变大,共模反馈环路只要M1~M4仍存在就会继续工作。若在输出范围的某一部分,运算放大器输出变得足够大能使M1~M4中的一个截止,则在那段输出部分共模反馈环路将不会正常工作。M1~M4在整个输出范围内仍存在的要求限制了运算放大器的输出范围。

2 改进的共模反馈结构

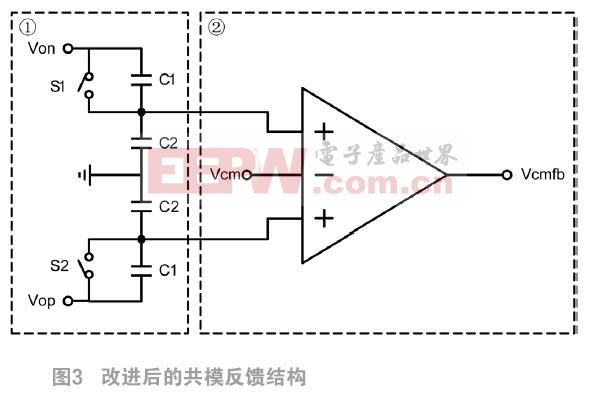

为了克服上述连续时间共模反馈电路输出摆幅受限和开关电容共模反馈电路共模电压建立缓慢、开关噪声注入较大的缺点,提出了一种新型开关电容共模反馈结构,该结构原理图如图3所示。

其中①部分称为输出电压缩放模块,②部分称为共模电平检测放大模块,②中的三端运放结构为图2中的共模反馈结构。Vcmfb是图2中的Vbias电压,反馈到差分运算放大器调节输出共模电平,S1和S2由同一时钟控制。

其工作原理如下:

在第一个时刻,开关S1和S2闭合,则电容C1被短路,此时要求全差分运算放大器的输入短路,以使输出差分电平为零,共模电平检测放大模块直接检测全差分运算放大器的输出电平,并反馈电压Vcmfb稳定输出共模电压至Vcm。

下一个时刻,开关S1和S2都断开,此时进入放大模式,全差分运放输出的电压变化通过电容C1和C2按一定比例缩放后,由共模电平检测放大模块(202)检测,并反馈电压Vcmfb至全差分运算放大器的电流源偏置点,稳定输出共模电压。

此新型开关电容共模反馈结构和传统的开关电容共模反馈结构相比,不需要使用非交叠时钟,开关数量减少,引入更低噪声,且在每一个周期共模电压都可以完全建立,建立时间不受限制。与传统的连续时间共模反馈结构相比,输出摆幅增加,也不会增加阻性负载。

3 仿真结果

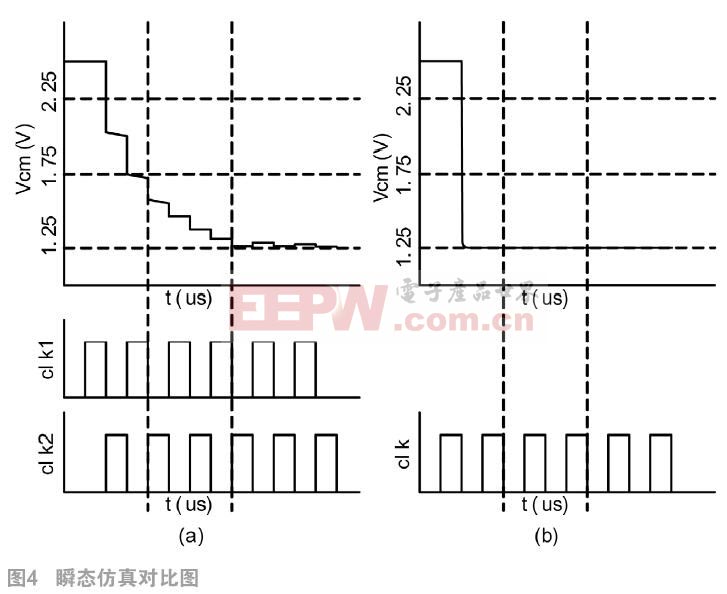

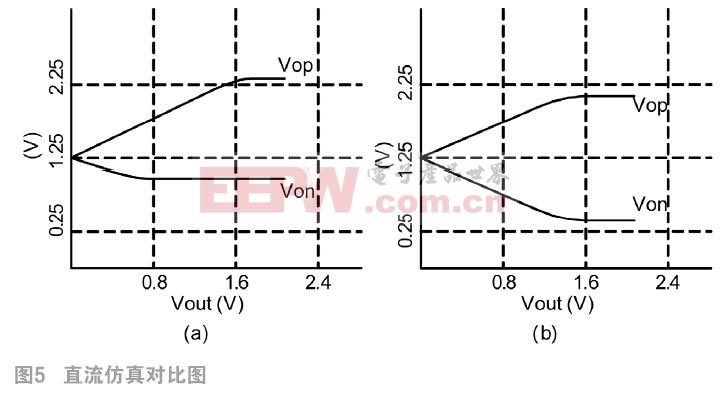

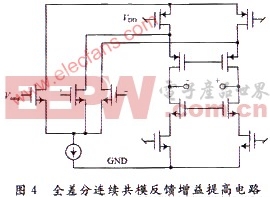

采用HLMC 40 nm CMOS 工艺设计了一款全差分运放并运用本设计提出的新型共模反馈结构,基于Cadence Spectre模拟器上对其进行仿真,仿真结果如图4(b)和图5(b)所示。同时给出了图1和图2中共模反馈的输出曲线图(图4(a)和图5(a))以作对比。

图4(a)为传统开关电容共模反馈瞬态仿真图,图4(b)为本设计的共模反馈结构瞬态仿真图,可以明显看出本设计的共模反馈结构的共模电压建立时间大大缩短,可以保障差分运放的快速正常工作。图5(a)为图2所示的传统连续时间共模反馈结构的直流仿真图,图5(b)为本设计的共模反馈结构的直流仿真图,仿真方法为在输入加入差分电压,得到输出电压值,从对比中可见,本设计共模反馈结构不会限制差分运算放大器的输出摆幅,可以在全输出范围内稳定输出共模电平。

4 结论

本文分析了传统共模反馈电路的原理及其存在的问题,提出了一种新的共模反馈电路,该电路克服了传统开关电容反馈结构对共模电平建立时间的要求,同时对差分运放的输出摆幅没有影响。采用HLMC 40 nm CMOS 工艺设计了一款全差分运算放大器进行仿真验证,结果表明该结构具有快速的稳定时间以及宽输出摆幅,可广泛应用于全差分运算放大器。

参考文献: [1]Mu feiyan, Wang Can, Lin Jie. A High- speed BiCMOS fully differential operational amplifier with improved slew rate and phase margin[C/OL].International Conference on Computer Science and Electronics Engineering(ICCSEE), 2012, March 23-25.

[2]Damiano C, Francesco C, Gianfranco A et al. A 94 dB 1.6 GHz SiGe fully differential operational amplifier using a novel classed AB output stage[C/OL].53rd IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Seattle, WA, Aug 1-4,2010.

[3]雷鑑铭,胡北稳.采用新型低成本共模反馈电路的全差分运放设计[J].浙江大学学报, 2013.

[4]宁宁,朱马.一种开关电容共模反馈结构.中国, 201210271855.9[P]. 2012-10-24.

[5]何杰,吴龙胜.一种新型开关电容共模反馈电路[J].电子技术, 2014.

[6]冯伟,戴宇杰.开关电容共模反馈电路建模与实现[J],南开大学学报, 2016.

本文来源于《电子产品世界》2018年第8期第58页,欢迎您写论文时引用,并注明出处。

评论