如何设计基于FPGA的虚拟现实定位系统?

虚拟现实技术是目前计算机信息科学中的前沿学科,文中设计了一种以FPGA 为核心的数据采集处理系统.利用HMC5883L和ADXL345对虚拟场景中物体的方位和朝向进行确定并通过以太网给虚拟场景主机发送数据.整个系统以 FPGA作为主控制器,配以传感器数据采集,内部FIFO存储,以太网高速传输,从而把定位系统参数实时传送到上位机中,具有传输速度快.实时性等优点,实现了虚拟现实高精度定位的功能.

本文引用地址:http://www.amcfsurvey.com/article/201808/385562.htm1 引言

虚拟现实(Virtual Reality,VR)是目前计算机应用方面活跃的技术研究领域,是整个信息科学领域中的新兴技术.它是依据计算机视频技术为基础,将计算机图像处理.计算机心理学.人工智能.人机交互技术.传感器技术.网络以及显示处理一系列信息技术分支的最新成果集中在一起.在虚拟现实环境中,人可以与虚拟世界中的场景和事物进行交互,它已经渗入到了航空航天.民用军事.娱乐游戏.医疗医用以及教育等行业.目前它已经是21世纪发展过程中影响人类生活的重要技术之一.

整个虚拟现实中,在场景中对物体的定位是关键核心部分.在定位中主要是要获得物体所处的直角平面坐标系中的朝向和位置以及物体与水平面的倾斜角.为此我们使用三维磁阻传感器和三轴重力加速度来获取所必须的数据.

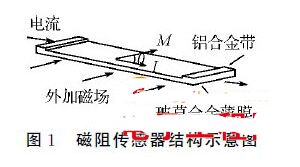

磁阻效应传感器是根据磁性材料的磁阻效应构成的.图1为简单的磁阻效应传感器的结构示意图.由于磁性材料(如坡莫合金)具有各向异性,对它进行磁化时,其磁化方向将取决于材料的易磁化轴.材料的形状和磁化磁场的方向.所以在其线性范围内,电桥的输出电压与被测磁场成正比.同时利用XYZ 三个方向上的磁通量进行三角函数的转换可知道方位角为X方向上与Y方向上面的反正切值.

三轴重力加速度传感器为多晶硅表面微加工结构,置于晶圆顶部.由于应用加速度,多晶硅弹簧悬挂于晶圆表面的结构之上,提供力量阻力.差分电容由独立固定板和活动质量连接板组成,能对结构偏转进行测量.加速度使惯性质量偏转.差分电容失衡,从而传感器输出的幅度与加速度成正比.相敏解调用于确定加速度的幅度和极性.

虚拟现实定位技术在国内外发展很迅速,主要在医疗与娱乐方面取得了成就.国内传统的技术主要是以单片机为核心处理器,在数据的处理和传输速度上有明显的不足.本文的虚拟定位系统利用高精度的定位传感器,FPGA处理和传输数据能够高速.实时的对数据进行采集与处理,降低了传输压力,提高了数据吞吐量与设备利用率.现场可编程逻辑门阵列FPGA,是现代IC设计验证的主流ASIC器件.FPGA设计灵活,易于修改,可靠性高,开发周期短,处理速度快,易于实现高速电路的设计,可以方便的对定位传感器进行驱动,并对其数据进行快速的处理和传输.

数据采集系统总体设计结构

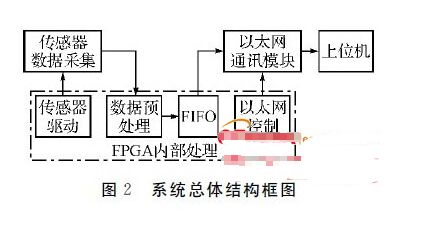

本文采用了Xilinx公司spartan3系列的 FPGA,ADI公司的ADXL345三轴重力加速度传感器以及Honeywell公司的HMC5883L三维磁阻传感器,利用了模块化的结构分别对每个单元进行流水线操作.整个系统主要包括:FPGA核心处理模块.硬件电源模块.场景数据处理模块.以太网通讯模块.当物体的方位角和倾斜角发生变化的时候,ADXL345模块和HMC5883L模块会将新的数据存储到FPGA中的FIFO里,最后通过以太网以UDP包的方式上传到上位机分析处理.系统中的接口电路主要有ADXL345与FPGA的接口.HMC5883L与FPGA的接口.以太网芯片与FPGA 的接口电路.系统上电以后,FPGA发出的信号包括两个传感器时钟驱动信号,以太网芯片控制信号.FPGA内部的信号包括FIFO控制信号.传感器信号传入的控制信号.系统的工作过程为:FPGA 对各传感器和以太网进行正确的驱动后,传感器开始以一定的频率向FPGA发送数据,当FPGA接收到一次数据后马上将数据存储在FIFO中;同时FIFO 在相应的条件下按照写时钟把数据一次存储好,按照时钟把原来存储的数据发送给以太网芯片;以太网芯片把这些数据封装成UDP包,通过以太网总线上传给上位机;最后,上位机在收到有效的数据时,对数据进行分析处理,然后传给三维软件部分使得三维场景中的物体也发生同样的方位角和倾斜角的变化,实现了虚拟现实的功能.

数据采集系统模块化设计

3.1 HMC5883L数据采集模块设计

场景数据模块是整个测量系统的基础部分,也是整个电路工作的必不可少的一个模块.其中包括了测量方位角用的HMC5883L磁阻传感器芯片以及测量倾斜角 的三轴重力加速度传感器ADXL345、HMC5883L是一种表面贴装的高集成模块,并带有数字接口的弱磁传感器芯片,应用于低成本罗盘和磁场检测领域.

HMC5883L的时钟是一系列的I2 C驱动时钟周期.本模块的设计目标在于将三维磁阻传感器芯片HMC5883L良好的驱动并确定时序中数据的传输顺序.目前采用FPGA引脚对相对应的时序进行控制.

HMC5883L传感器固定的时序中完成对数据的采集,采集到的数据是具有特定格式的数字量,需要经过一定算法分析和数据整理才能送往上位机进行操作. FPGA 与HMC5883L的通信采用了I2 C的通信手段,在代码编写的过程中采用了标准速率模式100kHz,在总线规定中,总线的位格式是一个8位数据/地址传送和1位应答位.如图3所示的格式 的时序情况.(点击可查看大图)

HMC5883L的工作流程:首先要芯片的初始化进行数据等待,之后使用I2C的传输方式对数据进行控制.一个测试前的过程需要对应有的测量寄存器进行对 应的配置.首先发送配置寄存器A的配置量,为写操作,寄存器指令为默认值;第二步发送配置寄存器B的配置量,同样也为默认值;第三步发送模式寄存器的配置 量,即发送数据0X00(即连续测量模式).此时配置的寄存器的流程已经走完.之后进入读操作模式,此时根据时钟的采样速度,循环对传感器内部寄存器 03-08进行操作,得到X、Y、Z 三个方向上的数据,读入到代码设定的寄存器中.具体操作流程如图4所示.

评论