关于英特尔“Foveros”逻辑芯片3D堆叠,看这两张图就够了 什么是“Foveros”逻辑芯片3D堆叠,英特尔答案在这里

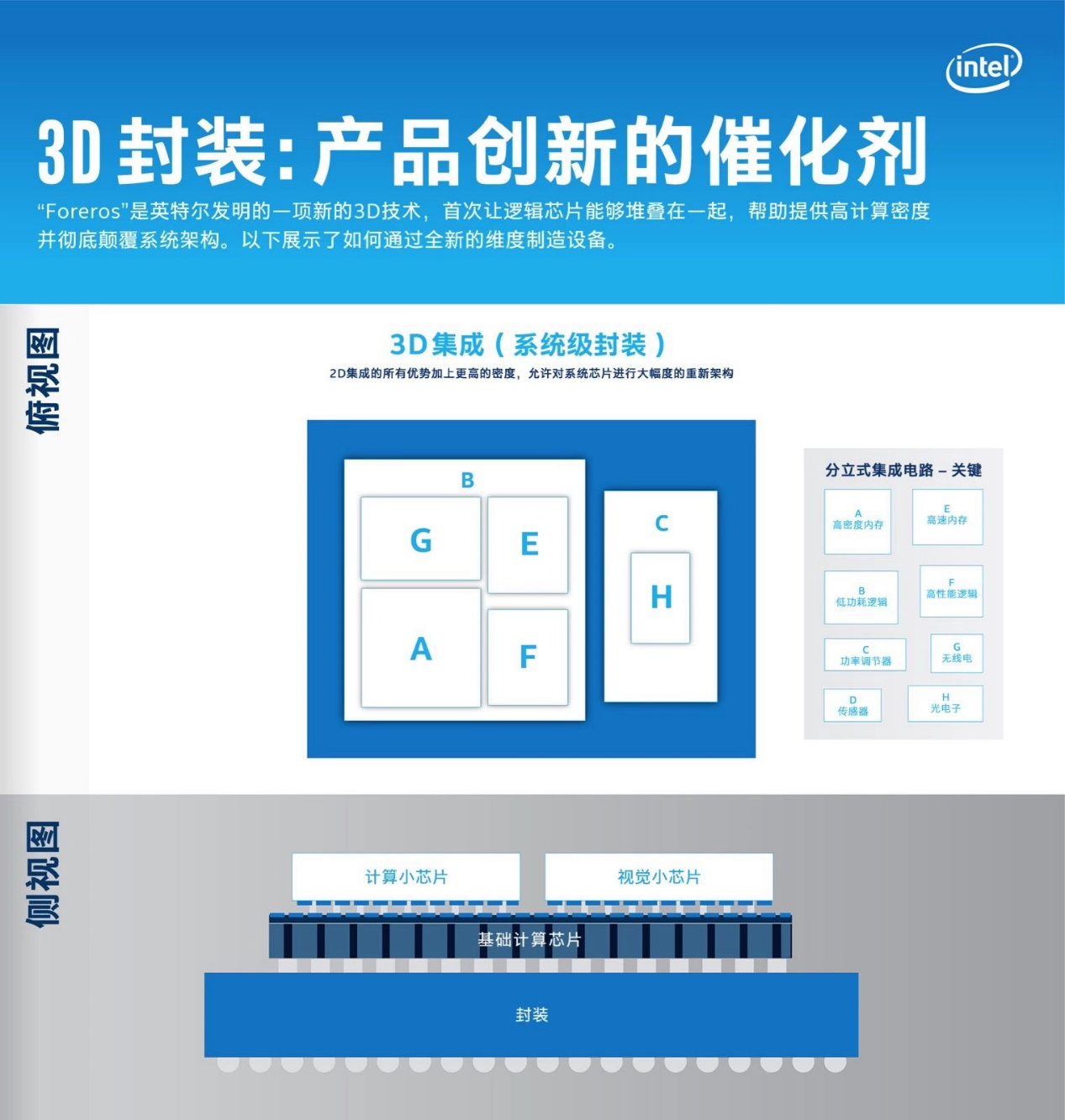

英特尔是全球半导体行业的引领者,以计算和通信技术奠定全球创新基石,塑造以数据为中心的未来,英特尔一直在不断追求创新发展。在近日举行的英特尔“架构日”活动中,英特尔不仅展示了基于10纳米的PC、数据中心和网络系统,支持人工智能和加密加速功能的下一代“Sunny Cove”架构,还推出了业界首创的3D逻辑芯片封装技术——Foveros。这一全新的3D封装技术首次引入了3D堆叠的优势,可实现在逻辑芯片上堆叠逻辑芯片。

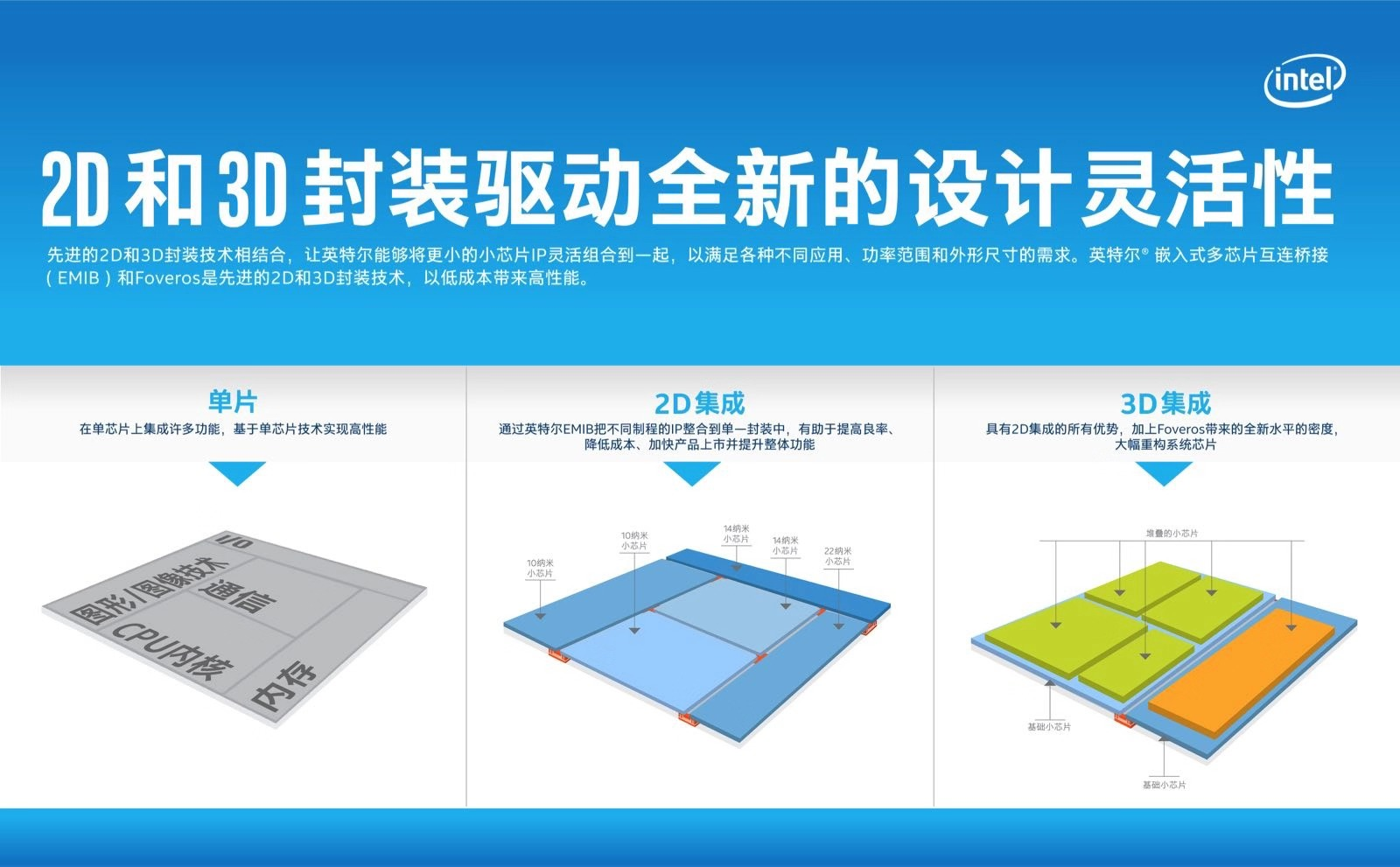

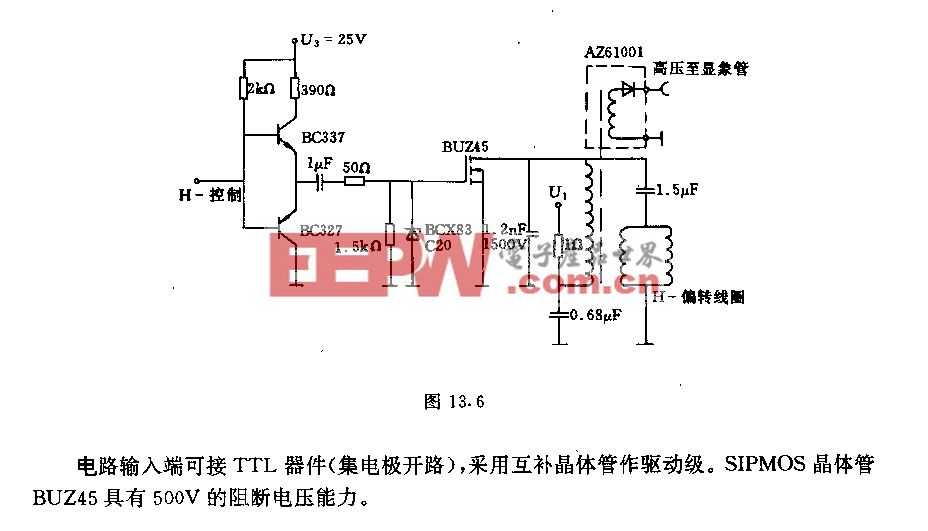

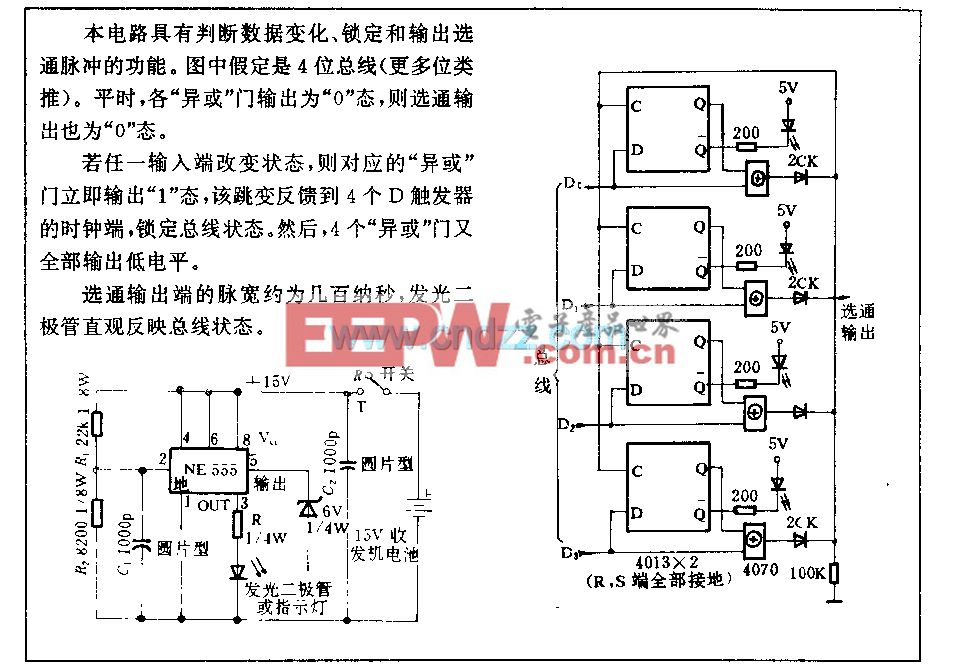

本文引用地址:http://www.amcfsurvey.com/article/201812/395624.htm以下两张图,是对这一突破性发明的详细介绍,第一张图展示了Foveros如何与英特尔®嵌入式多芯片互连桥接(EMIB)2D封装技术相结合,将不同类型的小芯片IP灵活组合在一起,第二张图则分别从俯视和侧视的角度透视了“Foveros” 3D封装技术。

据悉,英特尔预计将从2019年下半年开始推出一系列采用Foveros技术的产品。首款Foveros产品将整合高性能10nm计算堆叠“芯片组合”和低功耗22FFL基础晶片。它将在小巧的产品形态中实现世界一流的性能与功耗效率。

一直以来英特尔从云、网络到边缘设备以及它们之间的一切,并帮助解决世界上最艰巨的问题和挑战。这次非常具有创造力的尝试,是继2018年英特尔推出突破性的嵌入式多芯片互连桥接(EMIB)2D封装技术之后, Foveros将成为下一个技术飞跃。

评论