看看国外厂商正在发力研究的这些新技术

每年十二月,在美国旧金山或华盛顿哥伦比亚特区其中一处举行的年度电子会议。此会议作为一个论坛,在其中报告半导体、电子元件技术、设计、制造、物理与模型等领域中的技术突破。这个会会议就是IEEE国际电子元件会议(International Electron Devices Meeting,缩写:IEDM)

本文引用地址:http://www.amcfsurvey.com/article/201812/395988.htm在每一界的IEDM上,全球工业界与学界的管理者、工程师和科学家将会聚集在一起讨论纳米级CMOS晶体管技术、先进内存、显示、感测器、微机电系统元件、新颖量子与纳米级规模元件、粒子物理学现象、光电工程、功率与能量收集元件、高速元件、制程技术、元件模型化与模拟。 会议也涵盖硅、化合物、有机半导体与新兴材料系统元件的讨论和简报。

在今年的IEDM上,我们看到以下新技术趋势:

三星力推下一代3nm GAA-FET

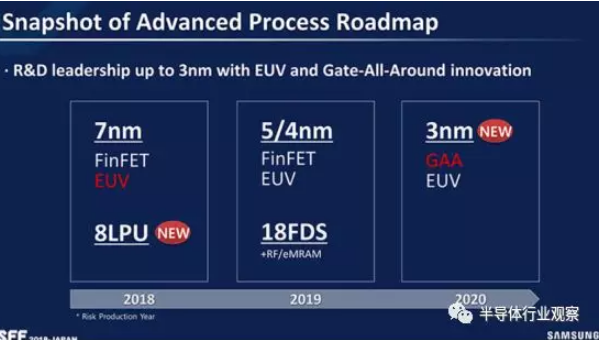

在今年五月份的Samsung Foundry Forum论坛上,韩国半导体巨头宣布了他们的工艺路线图。按照三星规划,其将首次采用EUV光刻(极紫外光刻)的7nm LPP(Low Power Plus)工艺技术将于今年下半年投产。关键IP正在研发中,明年上半年完成;7nm之后将会是其5nm LPE(Low Power Early),能实现更大面积的电路缩放和更低的功耗;在这之后,便会迎来4nm LPE/LPP制程工艺,这也是三星最后一次应用高度成熟和行业验证的FinFET立体晶体管技术。

三星路线图

在3nm的时候,三星计划引入了Gate-All-Around(简称GAA),也就是环绕栅极。相比于现在的FinFET Tri-Gate三栅极设计,这个重新设计了底层结构的晶体管能克服当前技术的物理、性能极限,增强栅极控制,获得性能大大提升。在日前的IEDM上,三星晶圆代工业务负责人表示,三星已经完成了3nm工艺技术的性能验证,并且在进一步完善该工艺,目标是在2020年大规模量产。

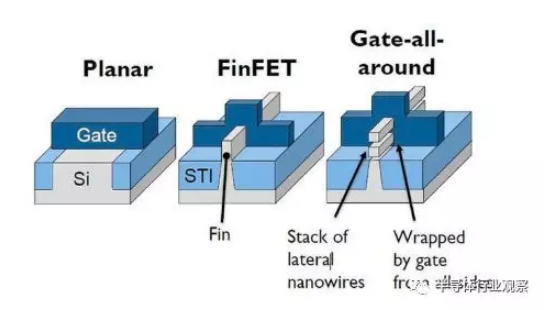

所谓Gate-all-around (GAA) ,有时候被称作横向纳米线场效应管。这是一个周边环绕着 gate 的 FinFet 。按照专家的观点, GAA 晶体管能够提供比 FinFet 更好的静电特性,可满足某些栅极宽度的需求,这主要体现在同等尺寸结构下,GAA沟道控制能力增强,因此给尺寸进一步微缩提供了可能;传统Finfet的沟道仅三面被栅极包围,而GAA以纳米线沟道设计为例,沟道的整个外轮廓都被栅极完全包裹住,这就意味着栅极对沟道的控制性能就更好。

从平面晶体管到GAA的演进

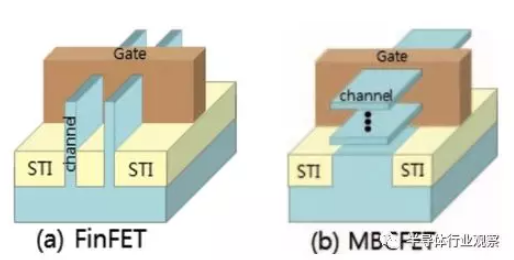

从Cadence博主Paul McLellan的文章我们可以看到,三星研究人员将将他们采用全环栅(GAA)晶体管设计的3nm CMOS技术叫做多桥通道(MBC)架构。据介绍,这个由纳米片(nanosheets)的水平层制成的沟道完全被栅极结构包围。

三星声称,这种技术具有高度可制造性。因为它利用了该公司现有的约90%的FinFET制造技术,而只需要少量修改过的光掩模。他们用它构建了一个功能齐全的高密度SRAM宏。他们表示,该工艺具有出色的栅极可控性(65 mV / dec亚阈值摆幅(subthreshold swing)),这比公司的FinFET技术高31%,且因为纳米片通道宽度可通过直接图案化来改变,这就给设计提供了灵活性。

在大家为晶体管的未来感到担忧的时候,三星给大家做了一个好指引。

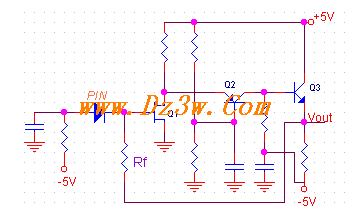

IMEC发布16nm DRAM

与CPU等芯片相比,DRAM内存在20nm节点之后也放缓了速度,线宽减少越来越困难,40nm工艺的DRAM内存芯片线宽减少约为5-10nm,20nm工艺的线宽减少就只有2-3nm了,更先进的工艺减少线宽就更困难了。能量功耗,带宽,延迟和制程升级成为了DRAM业者关注的重要问题,这也让厂商举步维艰。

以三星和SK海力士为例,据台湾媒体Digitimes在今年五月的报道,韩国两大存储巨头的18nm制程双双出现了良率问题,并遭到数据中心客户退货,且在改善前将暂缓出货,受到影响的业者包括亚马逊及阿里巴巴、腾讯、华为等大厂,台湾地区业者也陆续于近1~2周内获得讯息。报道进一步指出,三星18nm制程并非第一次传出质量疑虑,先前已修改过2次设计,原本业界以为第3次改良将可安全过关,不过高阶服务器产品应用于数据中心的要求较为严格,环境测试也较为严峻,在DRAM制程持续微缩下,导致符合规格的产品良率较难稳定控制。

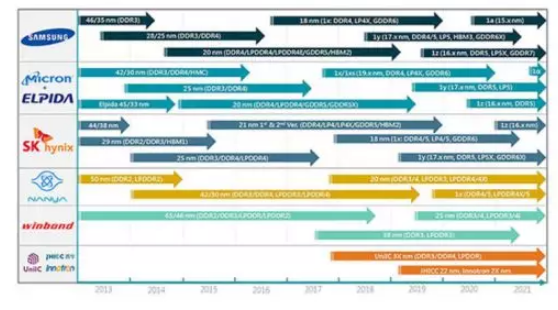

在18nm已经如此艰难,但专家认为20nm以下,DRAM工艺预计将经过两到三次的技术迭代,可以称之为1x nm,1y nm,1z nm。其中,1x nm位于16nm和19nm之间,1y nm则定义为14nm到16nm,1z nm则是12nm到14nm。随著而来的晶体管泄漏电流等问题就成为了悬在开发者头上的达摩克利斯之剑。

DRAM技术演进图,几乎所有厂商的1X、1Y和1Z路线图都延期了。

评论