一种基于电源管理芯片的新型欠压保护电路

A novel under-voltage protection circuit based on power management chip

本文引用地址:http://www.amcfsurvey.com/article/201903/399034.htm李宏杰,李立

(安阳工学院 电子信息与电气工程学院,河南 安阳 455000)

摘要:针对传统电源管理芯片中的欠压保护电路,提出了一种新型低温漂、低功耗、高精度的欠压保护电路。采用新型无电压比较器的欠压保护电路架构,通过基准自偏置产生的无温度系数电流与电源采样电流进行比较,进而对芯片系统各模块实现欠压保护。基于UMC0.25 μm BCD工艺库进行设计,采用HSPICE仿真软件进行分析。仿真结果表明:在电源电压上升沿过程中,当电源电压低于阈值电压3.85 V时,欠压保护电路输出高电平,芯片系统被关断;在电源电压下降沿过程中,当电源电压低于阈值电压3.63 V时,欠压保护电路输出高电平,芯片系统被关断。上升沿和下降沿的回差电压为0.22 V。满足电源管理芯片低温漂、高精度、低功耗的要

求。

关键词:欠压保护;电流比较;阈值电压;回差电压

*基金项目:河南省科技攻关项目(172102310671);教育厅科学技术研究重点项目(15A510017)

0 引言

欠压保护(under-over lockout,UVLO)电路是电源管理芯片中一种重要的保护电路,能够对供电电压进行检测,当供电电压低于系统预设临界值时,芯片系统部分模块会被关断,防止芯片系统输出逻辑错误和其他不良影响,因此欠压保护电路被广泛应用在电源管理芯片中的误差放大器、振荡器、电流检测等模块中 [1] 。

传统电压保护电路通常采用电压比较器架构,通过对带隙基准电压与电源采样电压进行比较,当电源采样电压低于基准电压值时,欠压保护电路输出高电平,芯片系统部分模块被关断;当电源采样电压高于基准电压值时,欠压保护电路输出低电平,芯片系统重新正常工作 [2] 。欠压保护电路的输出级采用施密特触发器和反馈控制回路产生迟滞电压,防止芯片系统由于电源电压波动被反复关断[3] 。虽然传统欠压保护电路原理简单、架构成熟,但是传统欠压保护电路需要带隙基准模块提供基准电压,并且需要电压比较器对带隙基准电压和电源电压进行比较,电路的功耗较大 [4] 。

本文基于UMC0.25 μm BCD工艺库设计了一种新型欠压保护电路,采用无电压比较器电路架构,通过基准自偏置产生的电流与电源采样电流进行比较,当电源电压低于系统预设值时,欠压保护电路输出高电平,芯片系统部分模块被关断;当电源电压重新高于预设值时,欠压保护电路输出低电平,芯片系统正常工作。输出级电路采用反馈控制电路产生迟滞电压,可以避免芯片由于电源波动反复关断。

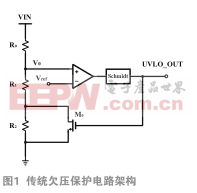

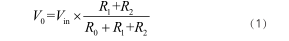

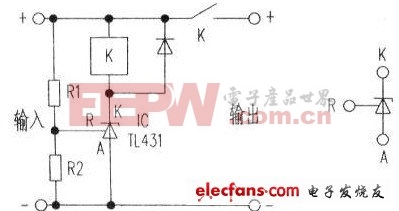

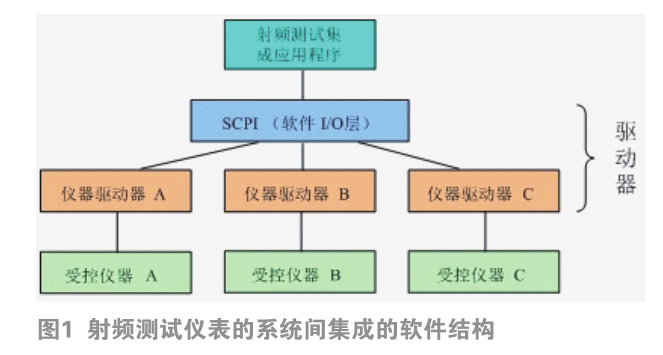

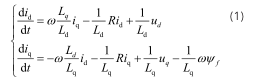

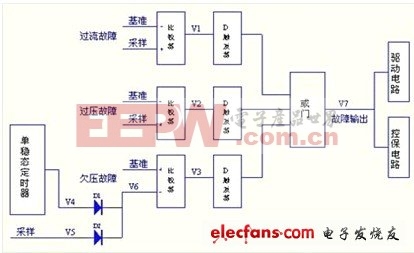

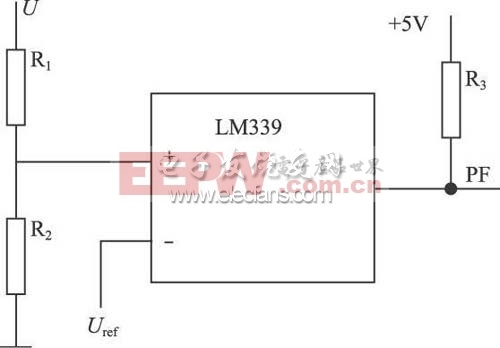

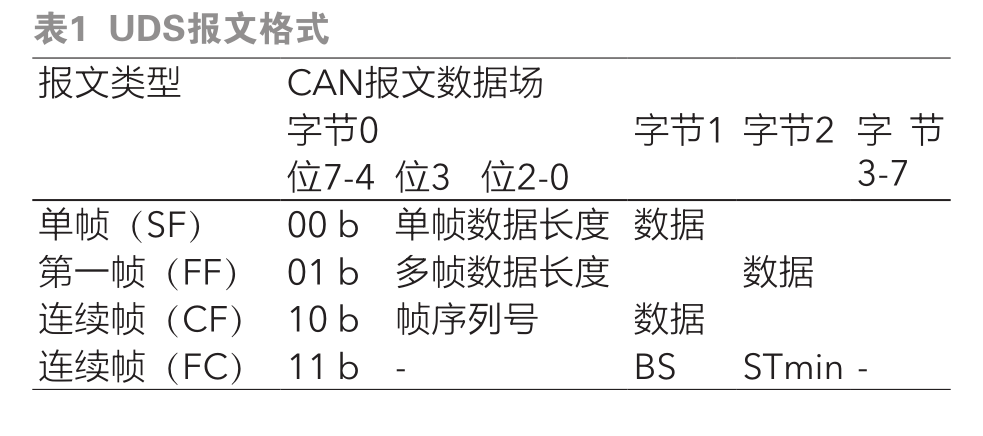

1 传统欠压保护电路原理及架构传统欠压保护电路如图1所示。其中,R0、R1和R2为采样电阻。由电阻串联分压原理可知,电源采样电压V0大小为:

电源采样电压V0和带隙基准电压VREF通过电压比较器进行比较,当电源采样电压V0低于带隙基准电压VREF时,欠压保护输出电压UVLO_OUT输出高电平,芯片系统部分模块被关断;当电源采样电压V0高于带隙基准电压VREF时,欠压保护输出电压UVLO_OUT输出低电平,芯片系统重新正常工作。欠压保护电路输出级采用施密特触发器和反馈控制电路产生迟滞电压,可以避免芯片系统由于电源波动反复关断。

虽然传统欠压保护电路架构成熟、原理简单,但是由于传统欠压保护电路额外需要带隙基准模块,电路功耗较大。同时需要电压比较器对电源采集电压和带隙基准电压比较,电路较为复杂[5] 。

2 新型欠压保护电路原理及架构

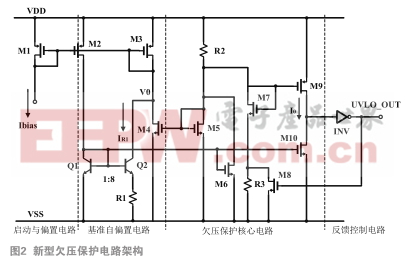

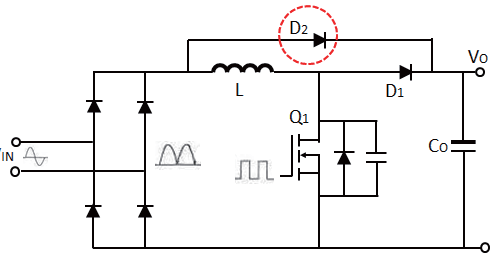

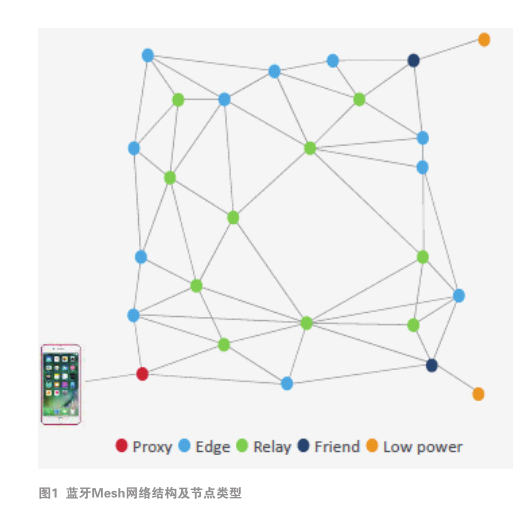

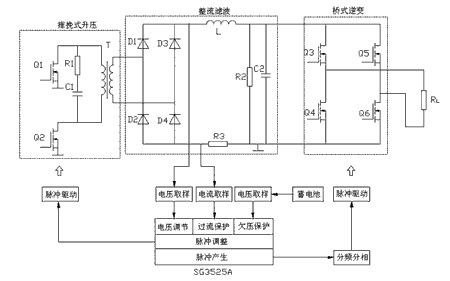

本文所提的新型欠压保护电路如图2所示。电路共分为启动与偏置电路、基准自偏置电路、欠压保护核心电路和反馈控制电路四部分。各部分电路工作原理如下:

2.1 启动与偏置电路

启动电路由晶体管M1~M3和偏置电流Ibias组成。当系统供电模块提供偏置电流Ibias为2μA时,欠压保护电路正常启动。M1~M3管构成的电流镜结构可以对偏置电流Ibias进行复制,通过调节各管子的宽长比可以调节电流的大小。启动电路为欠压保护电路,其他模块提供合适的偏置电流。

2.2 基准自偏置电路

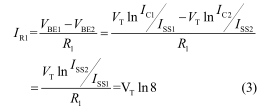

基准自偏置电路由Q1、Q2和R1组成。其中Q1和Q2是发射结面积之比为1:8的NPN晶体管。由半导体物理知识可得:

因此,流过电阻R1的电流IR1大小为:

其中,ISS为晶体管发射结的饱和电流,其大小正比于发射结面积[6] 。M4晶体管的漏极电压为:

由 双 极 型 晶 体 管 VBE的 温 度 特 性 可 知 ,

因此选择合适的电阻R1,就可以使V0点的电压为无温度系数。

2.3 欠压保护核心电路

欠压保护电路由晶体管M4~M10、R2和R3组成。其中R2和R3构成电源电压采集电路。当电源电压VDD发生变化时,通过电源采样电阻R2和R3采样出与之成正比的电流I0,其大小为:

M7和M9构成的电流镜把I0复制到UVLO_OUT端。I0与无温度系数的电流IR1在UVLO_OUT端进行比较。当I0<IR1时,欠压保护输出电压UVLO_OUT为高电平;当I0>IR1时,欠压保护输出电压UVLO_OUT为低电平。

2.4 反馈控制电路

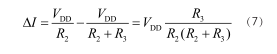

反馈控制电路由R2、R3和M8组成。当欠压保护电压UVLO_OUT输出高电平时,M8管栅极为高电平导通,R3被短路。此时的电源采样电流I0大小I0=VDD/R2。为回差电流DI大小为:

3 仿真结果及分析

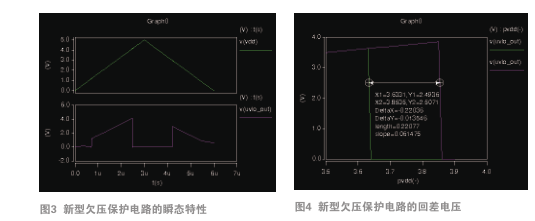

本文提出的基于电源管理芯片新型欠压保护电路采用UMC0.25 μm BCD工艺库设计,利用HSPICE仿真软件进行仿真,仿真结果如下:

图3为本文提出的新型欠压保护电路的瞬态特性仿真曲线。从图中可以看出,当电源电压VDD由小变大或由大变小过程中,当VDD小于上升沿和下降沿的门限电压值时,UVLO_OUT输出高电平,此时芯片系统部分模块被关断;当VDD大于上升沿和下降沿的门限电压值时,UVLO_OUT输出低电平,此时芯片正常工作。并且上升沿和下降沿的门限电压不一致,存在回差电压。

图4为本文提出的新型欠压保护电路的回差电压仿真曲线。从图中可以看出,电源电压上升沿的跳变门限电压为3.85 V,下降沿的跳变门限电压为3.63 V,回差电压△I为0.22 V。可以有效的避免芯片系统由于电源电压波动而出现的反复关断。

4 结论

本文提出了一种基于电源管理芯片的新型欠压保护电路。采用无电压比较器电路架构,通过基准自偏置电路产生的无温度系数的电流与电源采样电流进行比较。当电源电压在上升沿或下降沿低于系统预设值时,欠压保护电路输出高电平,芯片系统部分模块被关断;当电源电压高于系统预设值时,欠压保护电路输出低电平,芯片系统重新正常工作。同时上升沿和下降沿的跳变门限电压之间设有回差电压,防止芯片系统由于电源波动而反复关断。本文设计的新型欠压保护电路满足电源管理芯片低温漂、低功耗、高精度要求。

参考文献:

[1] 李艳丽,冯全源. 一种低温漂的欠压保护电路设计[J]. 电子技术应用,2014(6):30-32.

[2] 王慧丽,冯全源. 一种结构简单的新型CMOS欠压保护电路[J]. 电子器件,2017,40(3):593-596.

[3] 湛衍,姚远,黄武康.一种电机驱动芯片的欠压保护电路的设计[J].电子器件, 2013,36(5):709-711.

[4] 王智鹏,杨虹一款无电压比较器的欠压保护电路[J].电子世界, 2012, 13:51-52.

[5] 王锐,唐婷婷.一种BiCMOS欠压保护电路的设计[J].电子科技, 2006, 10:76-78.

[6] 唐宇,冯全源.一种低温漂低功耗带隙基准的设计[J].电子元件与材料,2014,33(2):30-33.

作者简介

李宏杰(1989-),男,硕士,讲师,主要研究方向:模拟集成电路设计。

李 立(1984-),男,硕士,讲师,主要研究方向:光电集成电路设计。

本文来源于科技期刊《电子产品世界》2019年第4期第46页,欢迎您写论文时引用,并注明出处

评论