比官方宣传还猛!台积电5nm晶体管密度比7nm提高88%

一般来说,官方宣传数据都是最理想的状态,有时候还会掺杂一些水分,但是你见过实测比官方数字更漂亮的吗?

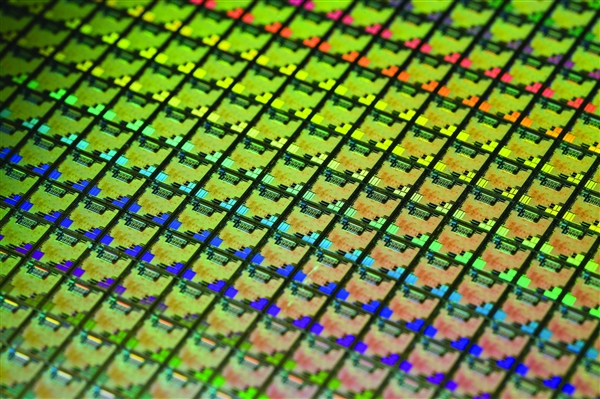

本文引用地址:http://www.amcfsurvey.com/article/202003/411258.htm台积电已在本月开始5nm工艺的试产,第二季度内投入规模量产,苹果A14、华为麒麟1020、AMD Zen 4等处理器都会使用它,而且消息称初期产能已经被客户完全包圆,尤其是苹果占了最大头。

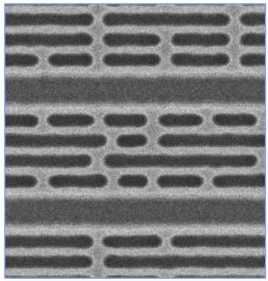

台积电尚未公布5nm工艺的具体指标,只知道会大规模集成EUV极紫外光刻技术,不过在一篇论文中披露了一张晶体管结构侧视图。

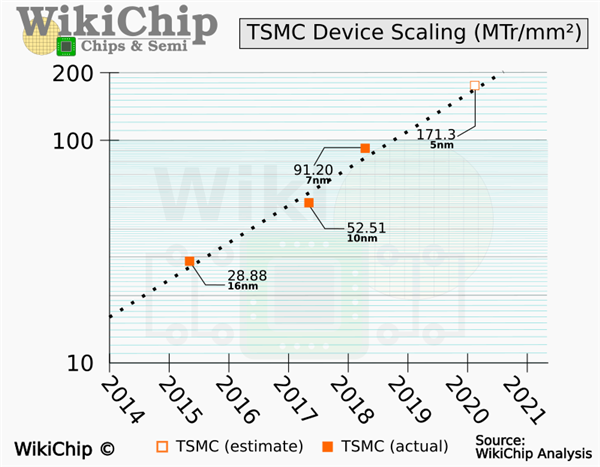

WikiChips经过分析后估计,台积电5nm的栅极间距为48nm,金属间距则是30nm,鳍片间距25-26nm,单元高度约为180nm,照此计算,台积电5nm的晶体管密度将是每平方毫米1.713亿个。

相比于初代7nm的每平方毫米9120万个,这一数字增加了足足88%,而台积电官方宣传的数字是84%。

虽然这些年摩尔定律渐渐失效,虽然台积电的工艺经常面临质疑,但不得不佩服台积电的推进速度,要知道16nm工艺量产也只是不到5年前的事情,那时候的晶体管密度才不过每平方毫米2888万个,5nm已经是它的几乎六倍!

另外,台积电10nm工艺的晶体管密度为每平方毫米5251万个,5nm是它的近3.3倍。

评论