微机电系统EMC达到99%改进幅度

本文阐述针对现今高度整合CbM解决方案因应EMC标准兼容性进行设计时所面临的关键挑战。EMC的设计颇有难度,即使是电路或实验室测试设定进行微幅变更都会大幅影响测试结果。本文说明一种系统层级EMC仿真方法或虚拟实验室,可协助工程师缩短时间内完成EMC兼容的设计工作。

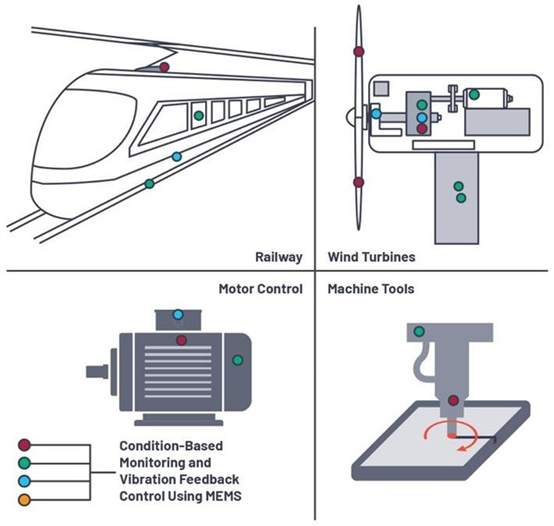

微机电系统广泛用于铁路、风力发电机、马达控制、工具机等环境中,目的是用于监测振动,藉以提升安全性、降低成本、以及尽力提高设备的使用寿命。MEMS传感器的低频效能,能比其他技术更早侦测出铁路与风力发电机应用的轴承损坏。大幅节省成本加上对各种设备瑕疵达到更高的侦测率,确保能符合各种严苛的安全标准。较宽的带宽(0 Hz至23 kHz)、低噪声性能、以及较宽的振动量测范围(2 g至200 g),这些都是振动侦测的必要条件。而这些目标全都可运用Analog Devices阵容广泛的MEMS产品轻易达成。

监测振动采用无线通信系统,用来和各处负责搜集原始数据的传感器进行通讯,或是利用原始数据执行实时控制。建置有线状态监测(CbM)系统面临许多挑战。其中一项关键挑战就是透过数公尺缆线运行时的电磁兼容(EMC)强固性,这类环境会受到包括间接照明电涌、静电放电、以及像是电感性或电容性负载切换等环境噪声。

因应EMC扰动能力不良,可能导致从CbM系统收集数据的质量出现间歇性或永久性的衰退,如图1所示。长久下来,质量不良的数据可能导致对资产健康与维护做出不正确的决策。

图1 : 有线式CbM系统链接振动传感器置于EMC干扰严重的工业环境

本文阐述针对现今高度整合CbM解决方案因应EMC标准兼容性进行设计时所面临的关键挑战。EMC的设计从一开始就极为困难,即使是电路或实验室测试设定进行微幅变更都会大幅影响测试结果。本文将介绍一种系统层级EMC仿真方法或虚拟实验室,其可协助工程师在创纪录的时间内完成EMC兼容的设计工作。

为何系统层级EMC仿真非常重要?

现代产品的开发时程包含同步进行的EMC兼容设计任务。针对EMC的设计应尽可能无缝衔接,但往往事与愿违,EMC问题与实验室测试经常会让产品上市延后数个月之久。虚拟实验室EMC仿真方法协助工程师解决各种EMC问题,其速度远快过仅采用实验室测试的方式。

在达成EMC兼容性方面,虚拟实验室模拟方法能解决关键问题,原因包括:

‧ 提高现代印刷电路板设计的整合度与组件密度,除了可能导致许多复杂问题,还会衍生许多EMC失效途径。模拟有助于判断最佳EMC抑制技巧,而且比光使用实验室测试的作法更加有弹性与省时。

‧ EMC标准的规范有时含糊不明,意谓若是以不同方法测试电路可能会出现不同结果。相较于实验室测试,使用模拟方法可迅速变更测试与获得结果。

‧ 整个系统需要在确保EMC兼容性的前提下进行开发,包含选用缆线的种类、长度、遮蔽,以及量测的设定。若是采用模拟法,实际量测时的探针效应就能忽略,而且更换缆线从以往费时数小时大幅缩短至数秒钟。

‧ 由于各家客户采用的受测设备不同,可能导致得到不同的测试结果。使用仿真法能更适切地模型分析与了解实际客户应用。

‧ 现有模拟工具并未统一,而且也没有针对缆线与电路板制定适用的仿真模型。虚拟实验室除了整合缆线、电路板、以及被动与主动组件模型,还能获得更准确的结果。

系统层级EMC仿真特性

系统层级EMC仿真透过以下各点特性,能够加快产品上市时程:

‧ 迅速找出电路弱点,提供针对性建议协助改进

‧ 找出EMC失效以及了解失效形成机制,这方面的工作成效能改进99%

‧ 大幅节省成本:无须执行反复的设计与测试尝试

‧ 大幅缩短时间:无须反复尝试多次设计方案,缩短数个月之久的开发时程,节省包括电路板线路配置、制造、组装的前置作业时间

EMC挑战

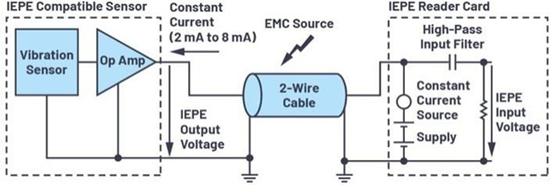

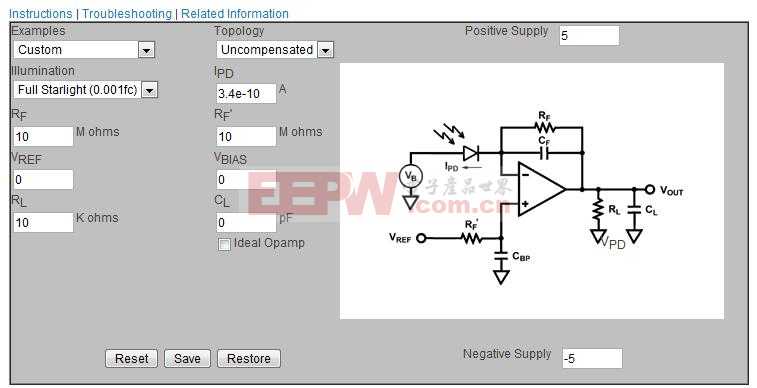

现今高度整合的传感器系统设计经常面临许多EMC挑战。首先,现代高整合度电路板设计让通过EMC测试成为艰难的任务。经常藉由共享电源与数据线架构(幻象电源)的作法来降低系统成本与电路板尺寸(较少的电路板链接)。振动传感器技术广泛采用的IEPE标准能为振动传感器提供恒定的电流源,并透过同一条线路读回传感器输出讯号,如图2所示。

图2 : 一个双线式IEPE传感器透过接口链接共享数据与电源架构

这种双线式系统意谓电源与数据通讯线会受到相同的EMC干扰,以致在针对EMC进行设计时会额外增加复杂度。EMC滤波组件必须审慎挑选以抑制各种电源干扰,但亦须避免降低数据电路的通讯带宽。

第二,系统层级EMC标准,像是IEC 61000-4-6传导射频抗扰性,针对许多工业产品所制定,制造商会标明产品的抗扰性达到Class A(没有通讯误差)或Class B(具有通讯误差,但系统不必重置)。各家制造商的Class A门坎会有差异,通常以位错误率(BER)或等价的微伏或micro-g来标示振动传感器的功能。

Class A兼容门坎通常会极低的电压,远低于系统能量测到的最小讯号。传导射频抗扰性标准让用户能用BER为系统定义通过/失败标准,以及规范设定细节与噪声拒斥位准。

最适合设定与BER需要深入探索,同时也成为系统设计者的一大挑战:如何让实验室设计验证测试设定能因应实际客户的应用,尤其是当测试设定的微幅变动可能导致测试结果出现巨幅变化。

第三,大多数常见EMC测试程序要求做出整个系统后,再送到EMC验证实验室进行测试。全系统包含挑选缆线、长度及遮蔽。不同缆线会有不同的电容规格,可能将更多或更少的EMC噪声耦合到受影响系统中。缆线长度与遮蔽接地可能导致在高EMC频率以及不同接地电流返回路径上出现阻抗不匹配的状况。

在建构系统时,较理想的测试方法是每个次单元单独进行EMC抗扰性测试; 然而在实际应用中,整个系统可能受到相同EMC噪声所影响。这些还只是一部分的原因导致厂方EMC测试很难对比客户实验室的测试。

由于现今各种高整合度设计与EMC测试的复杂性,促使业界需要一种能节省时间的弹性设计模式。在实验室测试之前进行模拟会是解决之道。目前锁定的目标是在耗费最少的时间与精力下取得正确的实验室数据。

运用虚拟实验室加快除错与解决EMC问题

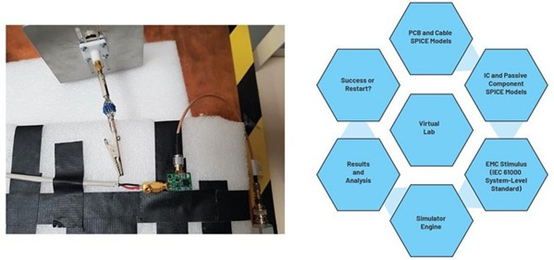

Analog Devices的系统层级专业与EMC模拟技巧促成虚拟实验室仿真流程,如图3所示。虚拟实验室环境让用户更容易首次上手就完成EMC设计,用户执行的是反复尝试虚拟设计,取代费时又昂贵的实验室设定与反复量测步骤。运算力、SPICE、电磁场仿真、以及CAD软件都达到成熟阶段,让这种虚拟实验室成为可行方案,让工程师现在可达到前所未有的精准度与仿真速度。电路板、缆线、整合电路芯片与被动组件都能建模分析,以及进行EMC模拟。除了分析结果,还能快速找出电路弱点以及提供针对性建议协助进行改进。

图3 : 从真实实验室转移至虚拟实验室环境

运用虚拟实验室环境,开发业者在测试过程中可存取系统任何实体节点,不会产生在实际实验室所面临的常见量测限制–像是量测设备带宽、实验室限制、探棒的非理想阻抗、以及外部噪声–这些都会对量测产生干扰。

在开始制造电路板之前仿真多项常见工业IEC 61000系统层级EMC标准测试,如表1所示。

MEMS与模拟案例研究

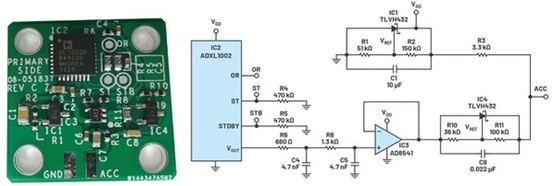

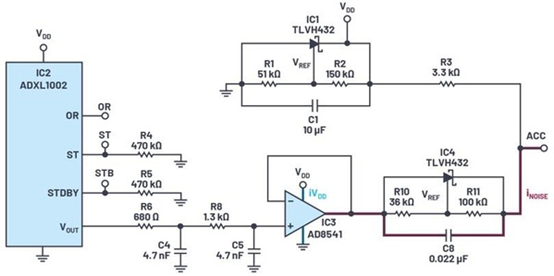

本节介绍模拟案例及与实验室量测的对比,图4的振动监测电路中采用Analog Devices的ADXL1002 MEMS加速计,这个电路兼容于广泛使用的IEPE接口,如图2所示。电路中含有两个分路调节器,其中一个(IC1)为加速计供电;另外,还有AD8541 运算放大器(IC3),以及第二个(IC4)提供9.5 V 直流偏压。当系统开始送电而ADXL1002为静态,通讯总线会在12 V dc 进行重置。图3的电路必须符合IEC 61000-4-6 传导射频抗扰性的标准,这项标准是工业应用设备的常见规范。

实际实验室对比虚拟实验室模拟,需要多个制程步骤:

1. 实际实验室设定对比模拟环境

2. 运用虚拟实验室开发仿真模型(如图3所示)

3. 运用模拟找出设计中的EMC弱点

4. 使用仿真找出设计问题以改进EMC性能

5. 在实际实验室中验证设计以改进EMC性能

关于制程步骤内容叙述如下:

步骤1 真实实验室设定对比模拟环境

IEC 61000-4-6传导射频抗扰性测试适用于在射频(RF)场环境中工作的产品。射频场会作用于连到安装设备的整段缆线。在EC 61000-4-6测试中,射频电压从150 kHz 步进到80 MHz。射频电压由1 kHz正弦波进行80%的振幅调变(AM)。IEC 61000-4-6 标准规范在10 V/m下Level 3为最高射频电压。射频电压注入到缆线遮蔽层,或用箝位电路(clamp)进行电容耦合。

如表2所示,虚拟与实际实验室环境需要对比几项关键参数:

‧ 测试位准与 IEC EMC 标准(振幅,频率)

‧ 缆线规格(长度、电容、遮蔽)

‧ 系统接地(包括缆线遮蔽)

‧ 量测参数 (电路中的组件与位置)

‧ 测试通过/失败门坎(振幅、频率)

步骤2 运用虚拟实验室发展仿真模型

通常厂商会提供大多数主动与被动电路组件的SPICE模型。电磁仿真器可仿真其他非标准组件,像是电路板几何与网络,以及缆线模型。

表2所搜集的信息协助确保精准模型分析缆线参数。这个系统采用双芯遮蔽线,成本高于无遮蔽线。没有遮蔽层让系统的EMC抗扰性较低。运用无遮蔽线进行仿真,结果显示EMC噪声远多过遮蔽式缆线系统。MEMS IEPE电路,如图4所示,尽可能设计成精巧尺寸(1.9 cm × 1.9 cm),只有2层PCB电路。使用2层PCB会增加潜在的EMC问题,因为有较高的耦合电容以及串音,因此必须小心设计。

图4 : MEMS 电路采用ADXL1002 与IEPE兼容接口

在这个时间点,系统设计工程师可以开始为PCB与缆线整理出模型,使用电磁仿真工具,将其连接到IC与被动组件的SPICE模型。之后再执行SPICE仿真,以及在系统层级与EMC仿真进行互动。

图5显示PCB物理几何与网络以及双芯遮蔽线的电磁模拟。三维电路板SPICE模型是PCB物理配置的完整抽象模型,包含许多针脚,可用来连结MEMS、运算放大器、以及分路调节器的SPICE模型。透过这种方式,可执行极精准的电气模拟。被动组件数据(电容、电阻、电感)都可以变更,系统响应可观察与修改,相较于变更与测试实际硬件的作法,可更快速且富弹性。缆线的SPICE模型也可在测试时进行模型分析–像是缆线长度可以增加或缩减,线长会对EMC耦合与系统效能有显著的影响。

图5 : 为电路板物理几何与网络以及双芯遮蔽线建立的电磁仿真模型,

完成EMC时域仿真后,工程师可分析在不同时间与频率下的电路瞬态响应。

根据EMC测试的种类,可执行瞬态或频率分析。许多瞬态分析的案例可用来执行抗扰性测试,另外频域的案例可用在幅射性电磁放射EMC测试(参考表1)。

步骤3 运用模拟找出设计的EMC弱点

一旦全系统完成模型分析与仿真后,就很容易找出失效机制。EMC噪声电压注入到缆线遮蔽层。噪声电压之后会耦合到缆线遮蔽层与线芯之间的寄生电容。噪声会传导到电路板上的ACC节点,如图6所示。

图6 : 电路失效机制

噪声电流会经过最小阻抗路径,这个案例中会经过运算放大器输出端的C8电容。运算放大器会饱和,将高电流抽出电源供应器(VDD)节点。IC1 VDD调节器无法供应这么高的电流; 因此VDD电压会下降。VDD 电压降会暂时关闭MEMS传感器(以5V额定电压供电),导致运算放大器输出端(噪声)出现电压涟波。

第二个失效模式也可找到,这个模式若是只用实验室测试法就很难甚至根本不可能观察到以及进行除错。高频传输线通常会用一个负载作为终端电阻,该负载的阻抗必须匹配传输线的阻抗。IEPE缆线由于属于低频率(kilohertz)数据通讯,因此通常没有终端接头。然而当注入60 MHz到70 MHz范围的噪声,由于缆线没有用匹配负载接上终端接头,因此噪声电压会在通讯总线上出现反射。

步骤4 使用模拟为设计找出改进EMC的潜力

目标是判断成本最小且最有效的电路变更方式来抑制EMC问题。如图7所示,只须加入两个电容就能解决两项EMC问题。22 nF CEMC 会将噪声带离敏感线路(运算放大器、MEMS),噪声电流现在会透过图中所示的C1电容分流到接地端。铁氧体磁珠(ferrite bead)在100 MHz频率下有高阻抗,可加入到电路中作为额外的确保,用来阻隔任何残除的噪声。CTERM则会在EMC测试时将高频率状态的缆线反射讯号分流出去。

图7 : 改进EMC性能的设计

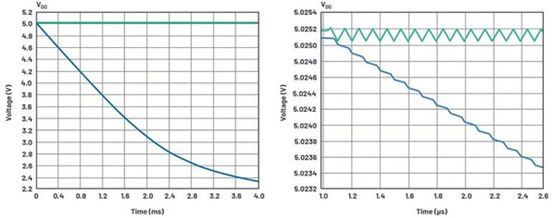

如步骤3所述,VDD 电源网络失效是反映EMC耐受性的一项可靠指标。图8显示VDD电源网络的电压降,这里没有使用CEMC。模拟结果预测约2V或更大的压降。当使用CEMC时,偏离额定值的幅度为微伏范围,远低于1.6 mV目标兼容门坎。

图8 : 仿真VDD电路网络,包括使用 CEMC 电容(上方绿色波形)与没有使用 CEMC (下方蓝色波形曲线)的状况

Analog Devices的ADXL1002 MEMS传感器在11 kHz下具有3 db带宽,因此选择CEMC与CTERM变得很重要,选择正确才能维护11 kHz通讯总线。利用虚拟实验室的弹性,除了可仿真多种电容值,还能挑选出两个最佳电容值。在加入这些电容后,系统会预测出低于1.6 mV噪声电压时通过EMC标准测试的能力。

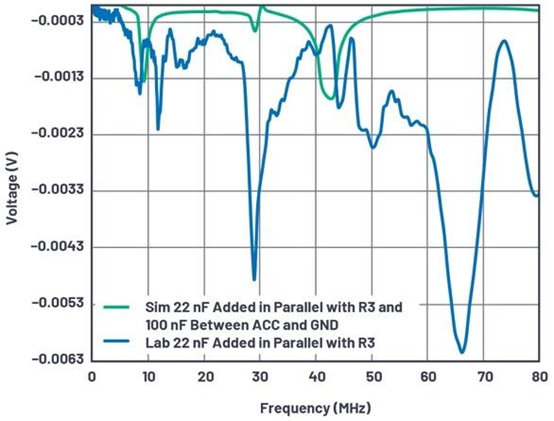

步骤5 在实际实验室中验证设计以改进EMC性能

如图4所示的原始电路使用表2的参数在实验室进行测试。结果在77 MHz测试频率下出现912 mV噪声的失败状况。经过步骤4的建议,加入一个22 nF 电容(CEMC)与R3电阻并联。结果得到99%的改进幅度,量测到的噪声低于6 mV,如图9所示的实验室测试结果(蓝色波形)。

为达到低于1.6 mV噪声的设计目标,在ACC与GND节点之间加入一个100 nF CTERM电容,以及22 nF的CEMC电容。图9显示绿色仿真结果,噪声曲线在0.15 MHz到80 MHz频谱区间呈现平坦走势。

图9 : 依循虚拟实验室的建议进行模拟与实验室测试的结果

在达成结果与目标后,就可以判断系统哪个部分是EMC的弱点。在这个案例中,缆线是主要成因,因为缆线会将EMC能量从来源端耦合到电路,加上因缆线的长度以及较高频率下的终端阻抗造成的讯号反射。

两个电容(CTERM与CEMC)能将两个噪声源有效分流到接地端。替代的解决方案与方法,像是更换运算放大器,都是不实际的作法。把运算放大器换成超低输出阻抗的运算放大器则是不理想的选择,因为输出阻抗较低的组件天生高耗电,从而影响整体设计的竞争力。

总结

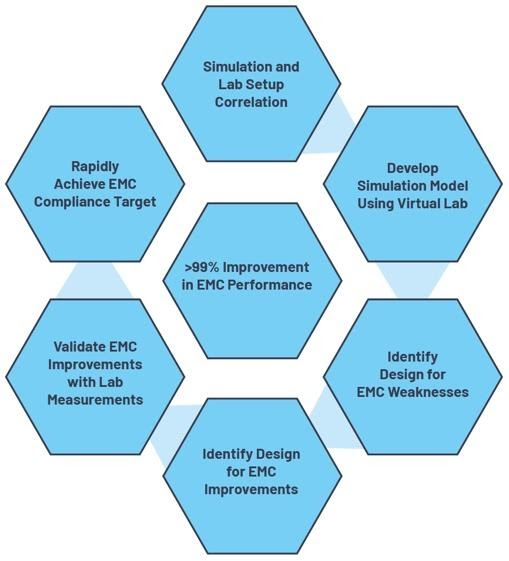

全系统仿真带来前所未有的洞察力,让业者掌握在EMC压力下电路的行为及解决各种复杂EMC问题的最佳办法。使用这种方法可大幅缩短产品的上市时程。运用本文介绍的制程流程,如图10所示,可以让设计的EMC性能获得超过99%幅度的改进。

图10 : 制程流程,让EMC性能获得超过99%幅度的改进。

(本文作者Ricardo Zaplana、Richard Anslow为ADI工程师)

评论