PCB传统四层堆叠的缺点

如果层间电容不够大,电场将分布在电路板相对较大的区域上,从而层间阻抗减小,返回电流可以流回顶层。在这种情况下,该信号产生的场可能会干扰附近改变层的信号的场。这根本不是我们所希望的。不幸的是,在 0.062 英寸的 4 层板上,各层之间的距离较远(至少 0.020 英寸,如图 1 和图 2 所示),并且层间电容很小。

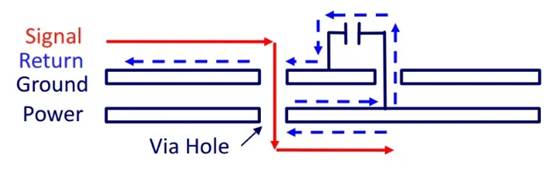

本文引用地址:http://www.amcfsurvey.com/article/202307/448419.htm当走线从第 1 层更改为第 4 层或反之亦然时,图 1 和图 2 中的层叠的个问题就会出现。如图 3 所示。

图 3.图片由Altium提供。

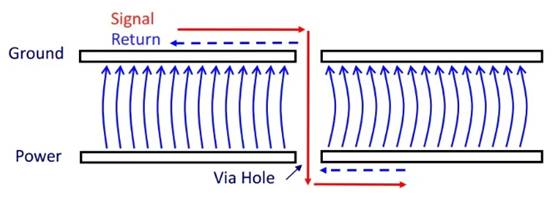

该图显示,当信号走线从第 1 层到第 4 层(红线)时,返回电流也必须改变平面(蓝线)。如果信号的频率足够高并且平面靠得很近,则返回电流可以流过接地层和电源层之间存在的层间电容。然而,由于缺少返回电流的直接导电连接,会导致返回路径中断,我们可以将这种中断想象为平面之间的阻抗(见图 4)。

图 4.图片由电磁兼容性工程提供。

如果层间电容不够大,电场将分布在电路板相对较大的区域上,从而层间阻抗减小,返回电流可以流回顶层。在这种情况下,该信号产生的场可能会干扰附近改变层的信号的场。这根本不是我们所希望的。不幸的是,在 0.062 英寸的 4 层板上,各层之间的距离较远(至少 0.020 英寸,如图 1 和图 2 所示),并且层间电容很小。因此,就会出现上述的电场干扰。这可能不会导致信号完整性问题,但肯定会产生更多的 EMI。这就是为什么在使用图 1 和图 2 所示的层叠时,我们避免更改层,特别是对于时钟等高频信号。

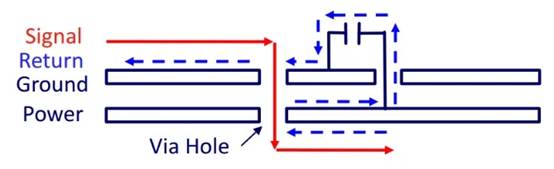

通常的做法是在过渡过孔附近添加一个去耦电容器,以降低返回电流所经历的阻抗(参见图 5)。然而,这种去耦电容器由于其自谐振频率较低,因此对于甚高频信号无效。对于频率高于 200-300 MHz 的交流信号,我们不能依靠去耦电容器来创建低阻抗返回路径。因此,我们需要一个去耦电容器(对于 200-300 MHz 以下)和一个相对较大的板间电容以用于更高的频率。

图 5 图片由Altium提供。

通过不改变关键信号的层可以避免上述问题。然而,四层板的小板间电容导致了另一个严重的问题:电力传输。时钟数字IC通常需要大的瞬态电源电流。随着 IC 输出的上升/下降时间缩短,我们需要以更高的速率提供能量。为了提供电荷源,我们通常将去耦电容器放置在非常靠近每个逻辑 IC 的位置。然而,存在一个问题:当我们超出自谐振频率时,去耦电容器无法有效地存储和传递能量,因为在这些频率下,电容器将像电感器一样工作。

由于当今大多数 IC 都具有快速上升/下降时间(约 500 ps),因此我们需要一个额外的去耦结构,其自谐振频率高于去耦电容器的自谐振频率。电路板的层间电容可以是一种有效的去耦结构,前提是各层彼此足够接近以提供足够的电容。因此,除了采用常用的去耦电容器外,我们更喜欢采用紧密间隔的电源层和接地层来为数字 IC 提供瞬态电源。

请注意,由于通用的电路板制造工艺,我们通常在四层板的第二层和第三层之间没有薄绝缘体。在第 2 层和第 3 层之间具有薄绝缘体的四层板的成本可能比传统的四层板高得多。

评论