加倍并减轻 PWM 的滤波要求

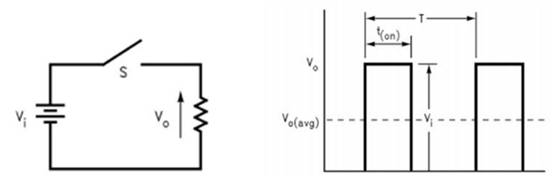

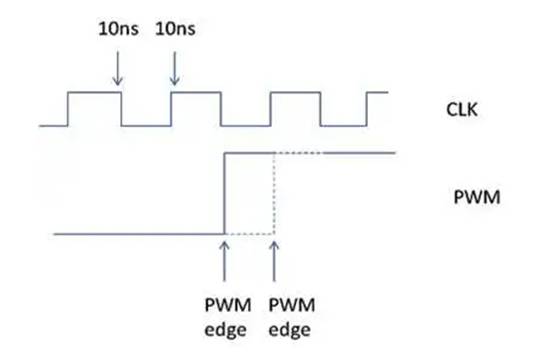

经典脉宽调制器 (PWM) 发出 H 个连续逻辑高电平(1),后跟 L 个连续逻辑低电平(0)的重复序列。每个高电平和低电平持续一个时钟周期 T = 1/F (Hz)。结果的占空比可定义为 H/N,其中 N = H+L 时钟周期。N 通常是 2 的幂,但 N 可以是任何大于 0 的整数。

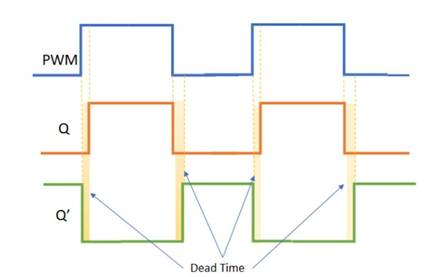

本文引用地址:http://www.amcfsurvey.com/article/202307/448701.htm经典脉宽调制器 (PWM) 发出 H 个连续逻辑高电平(1),后跟 L 个连续逻辑低电平(0)的重复序列。每个高电平和低电平持续一个时钟周期 T = 1/F (Hz)。结果的占空比可定义为 H/N,其中 N = H+L 时钟周期。N 通常是 2 的幂,但 N 可以是任何大于 0 的整数。 PWM 必须面对的一个挑战是通过过滤流的动态 AC 部分进行衰减,同时保留其平均 DC 值。在整个输出序列范围内,经典 PWM 的频率分量 F/N 也是的,因此难衰减。幸运的是,这个设计理念引入了一个简单的技巧,可以缓解这一挑战。

在讨论这个技巧之前,有必要快速回顾一下其他交流能量缓解技术,所有这些技术都像经典技术一样,采用某种计数器作为其驱动引擎。我几年前读过但找不到参考的一种方法涉及 N = 2 M -1 状态的 M 位伪随机序列生成器,其每个位都连接到数字比较器的一个输入 [1]。剩余的输入以数字W表示。当生成器的数量小于W时,比较器输出1;当生成器的数量小于W时,比较器输出1。否则,输出零。当发生器被计时时,结果是 W 个 1、N-W 个 0 和 W/N 占空比的随机流。结果的频谱“白噪声”性质比传统 PWM 的 F/N 主要成分更容易过滤。

一些 SAM D Microchip 微控制器的硬件中内置了更有效的缓解措施 [2]。这些 PWM 修改8 位经典 PWM 序列的2 X 个连续周期,以产生长度为 2 X+8的更长重复序列。这里 X = 4、5 或 6。对于 K / 2 X+8的占空比,0 ≤ K < 2 X+8,每个八位序列至少具有 K/2 X的整数部分。剩余的 K 个模 2 X尽可能均匀地分布在 2 X八位序列中。结果是占空比调制的八位序列的长序列,在频率 F/2 X+8处或附近具有非常小的频谱能量生成的 Hz 大部分位于 F/2 8附近,并且滤波问题得到了简化。

这些方法的硬件支持并不总是可用。幸运的是,大多数微控制器都可以轻松实现上述技巧,其描述如下。一旦完成 N = 2、3 或 4…多 2 8 个(甚至 2 16 个)状态计数器驱动 PWM 的初始设置,无需软件干预“设置它(占空比),然后就可以忘记它” PWM操作触手可及。当占空比确实需要改变时,所需的 H 值被写入输出比较寄存器 (OCR)。在大多数情况下,两个具有独立占空比的 PWM 可用,通常由同一计数器驱动。考虑一下利用这些功能组合可以实现什么目标。

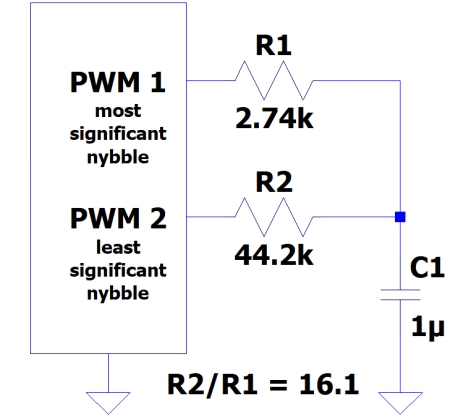

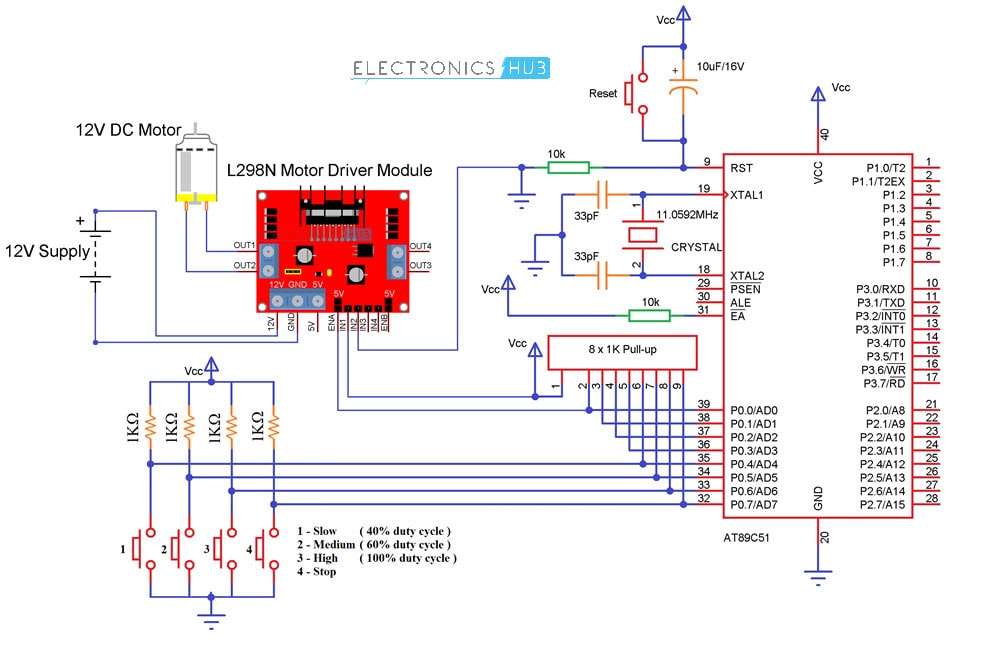

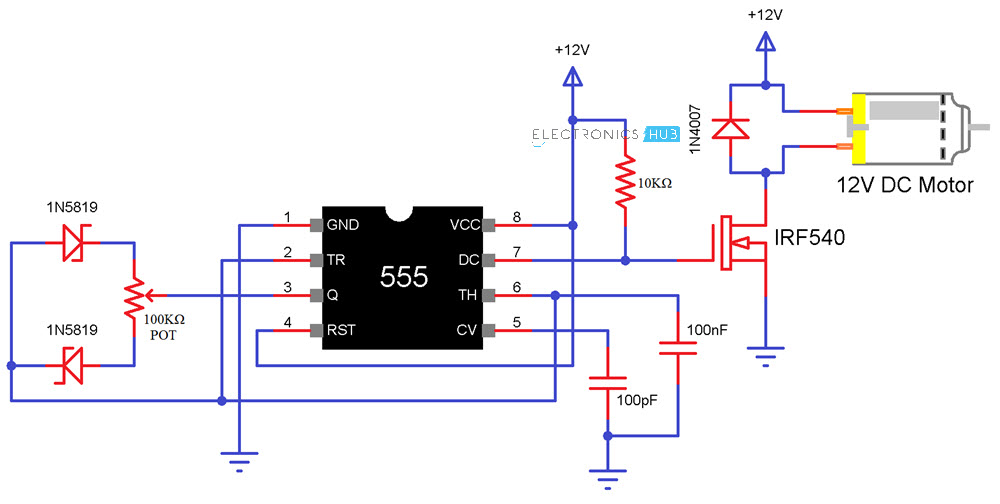

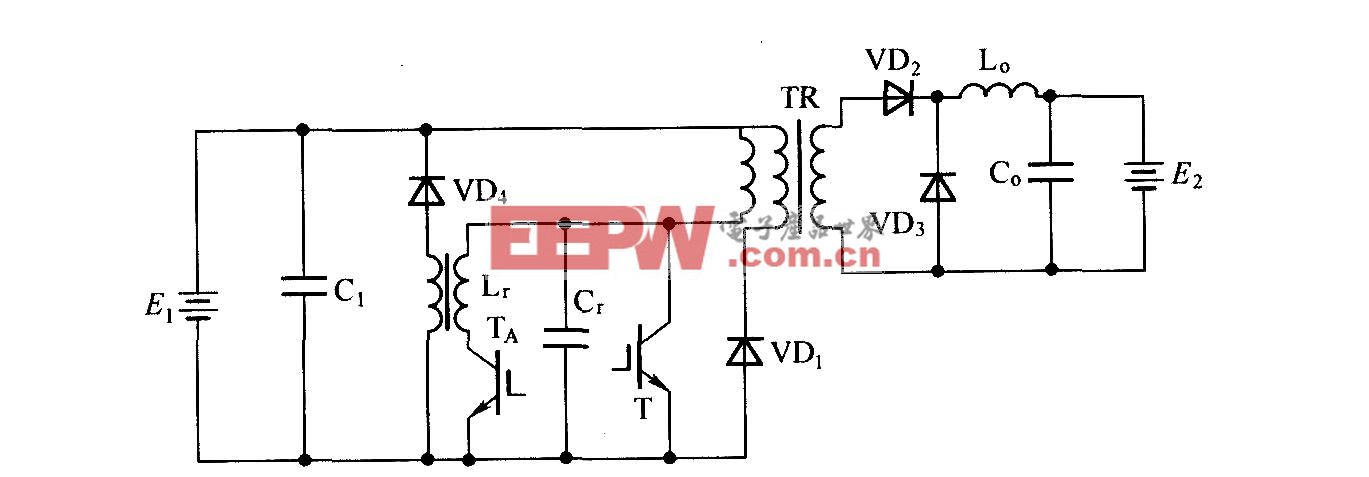

在一个示例中,计数器可配置为 N = 16。 PWM 的占空比可为 1/16、2/16、3/16,一直到 15/16。剩余状态将为 0/16 或 16/16。两个 PWM 输出由两个电阻按 1:16 的比例串联组合连接。在这两个电阻的连接处,有 2 4 ×2 4 = 2 8个可能的平均值,就像单个 PWM 呈现 2 8个不同状态一样。影响交流衰减的简单方法是在该结点和地之间连接一个电容器(图 1是完整电路的示例。)

图 1完整电路代表了实现交流衰减的简单方法,其中电容器连接在 PWM 输出端的两个电阻器与地之间的连接点之间。

但这种技术和传统 PWM 都可以受益于更复杂的网络,该网络具有更多数量的电阻器和电容器,甚至还可以选择使用运算放大器来缓冲结果。运算放大器还可以实现包含复杂极点对的滤波器,而不是仅限于实极点,实极点是可获得的极点。前一种类型更有效地化滤波器稳定时间和残余交流能量大小的乘积。(早期的设计理念中已经给出了这样的一个例子。)

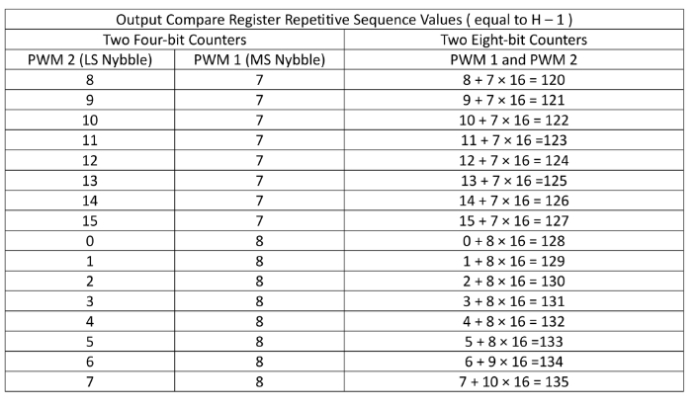

我使用 ATmega16 微控制器来实现图 1 电路。尽管可以使用更高的时钟频率,但 F 设置为 1MHz。PWM 1 和 PWM 2 配置为以两种不同的模式运行:前面描述的两个四位单元具有独立值的输出,以及作为具有相同输出的八位单元。这对于两种操作模式都保持相同的 RC 滤波器时间常数。表 1列出了每种模式的 OCR 重复序列。

表 1四位和八位 PWM 模式用于生成图 2 波形的 OCR 值。

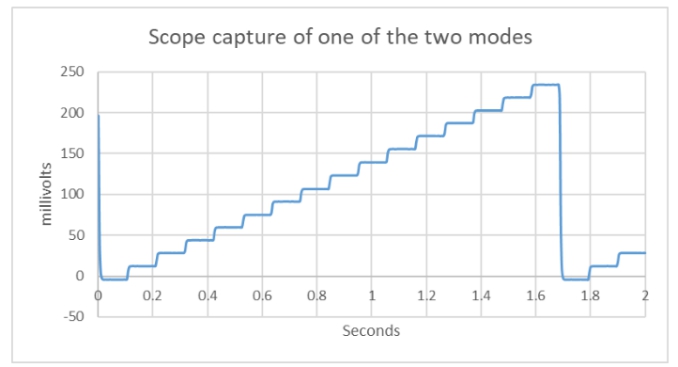

图 2显示了两种模式之一的示波器捕获;两种模式的屏幕截图无法区分,分辨率约为 18 mV。(必须在 R1-R2-C1 结点和负直流电压之间连接一个额外的电阻(未显示)。在不影响 R1-R2 比率的情况下,这会将波形的电压移至接近接地的电压,以便示波器可以显示它具有高分辨率。)

图 2通过对表 1 中列出的四位和八位 PWM 模式的 OCR 进行编程而生成的波形。两种模式的结果看起来相同,因为示波器以 200 ms/div 扫描速率平均交流能量。

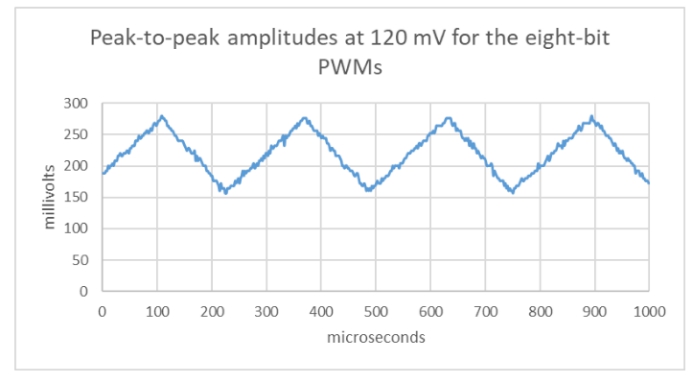

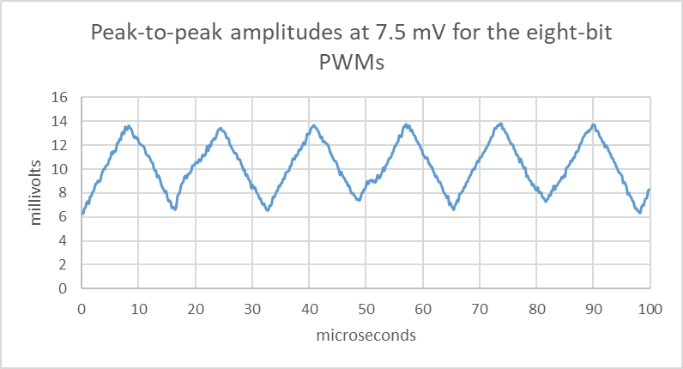

两个四位 PWM 的频率均为 F/16 = 62.5 kHz;八位的频率为 F/256 = 3.90625 kHz。该代码大约每 100 毫秒更改 OCR 寄存器。在图 2 的扫描速率下,示波器滤除 PWM 交流信号,并将其替换为平均值。在随后的图中,示波器以更快的扫描速率显示了它们的峰峰值幅度。图 3显示 8 位 PWM 的电压为 120 mV,而图 4显示 4 位 PWM 的电压仅为 7.5 mV。

图 3图 1 八位 PWM 电路中电容器两端的交流能量。

图 4图 1 电路中四位 PWM 电容器两端的交流能量。四位 PWM 的周期和幅度比八位 PWM 小 16 倍。

两种模式的步进分辨率均为 18 mV,四位峰峰值噪声在不到半步的情况下接近;任何更多的交流信号衰减都会不必要地增加 1 ms 半步稳定时间。在 1/16 频率下峰峰值为 120 mV(6.7 步长)时,八位 PWM 实现几乎无法使用。电容器值必须增加到 15μF,相关的稳定时间增加 15 倍,才能满足双四位 PWM 方法的能量衰减性能。

本示例中采用的方法非常强大。通过一对与 0.1% 电阻互连、比率为 256:1 的 8 位 PWM,(双八位)16 位 PWM 可以具有比传统 16 位 PWM 更容易过滤 256 倍的交流输出。位单位。小于 N = 2 16或 2 8级的 PWM 分辨率也可以同时减少 PWM 周期并简化相关的滤波要求。甚至还有带有三个或四个 PWM 的微控制器,其输出可以与合适的电阻网络相加

评论