第六代Spartan FPGA迎接智能边缘互联新挑战

预计到2028年,物联网设备的数量将增加一倍以上,处理能力需求也将同步增长。设备数量的激增会推动产生对于更高数量I/O的需求、对更通用I/O的需求,以及对于边缘端安全解决方案的需求;处理能力需求的提升则需要更强且更有效率的处理器,这些需求的驱动下,经济型FPGA迎来了全新的市场发展机遇。

作为经济型FPGA的经典系列,从1998年Spartan FPGA首发以来持续推动着包括日常所使用技术的进步以及医疗机器人和宇航探索等很多突破性的进展,特别是最近这些年在诸多边缘互联应用中收获了广泛的应用场景。在总结Spartan FPGA为何如此受推崇时,AMD自适应和嵌入式计算事业部成本优化型芯片营销高级经理Rob Bauer直言,因为AMD把很多前瞻性的产品特性跟比较小型化的器件的尺寸规格、较低的密度和较优化的成本进行了出色的结合。

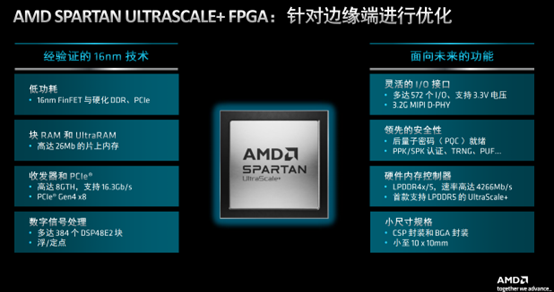

现在AMD推出了全新的第六代Spartan FPGA产品,在设计新一代Spartan UltraScale+ FPGA 系列的时候,AMD根据市场需求的变化提供了非常高的I/O的密度,低功耗和极为领先的安全功能,Rob Bauer坦言这将让客户可以在更小的器件上实现更多的功能,同时能够去降低总成本占地的面积、体积,还有功耗。同时,新一代的Spartan UltraScale+ FPGA 系列产品采用了经业界验证的16纳米FinFET制程工艺,相比于上一代28nm工艺可以让器件实现高达30%的功耗降低。依靠UltraRAM存储的支持,新一代产品片上内存总数也得到增加,同时具有更快的收发器速度,其高达16.3 Gb/s,辅以PCIe4硬化功能,从而提供更快、更高效的数字信号处理能力,它的速度可以多达384个DSP48E2块。新的Spartan UltraScale+ FPGA提供了三种不同类型的I/O,可以支持MIPI D-PHY协议,多达572个I/O,支持3.3V电压,3.2 G MIPI D-PHY。此外,AMD也对相关的互联IP进行了硬化,例如DDR内存和PCIe,这样就能让逻辑单元更好地运行,进一步实现接口效率提升与降低功耗。

边缘端安全性现在对客户越来越重要。第六代Spartan UltraScale+ FPGA系列提供了AMD 成本优化型FPGA产品组合中最多的安全功能,比如后量子密码技术(PQC)和AES-GCM,这些用于比较高速安全的配置和物理不可克隆功能(PUF),进一步减少单一事件干扰(SEU)造成的威胁。其中,支持后量子密码技术并具备获 NIST 批准的算法,能提供先进的 IP 保护,抵御不断演进的网络攻击和威胁。物理不可克隆功能会为每个器件提供唯一指纹,以提升安全性。PPK/SPK 密钥支持有助于管理过期或受损安全密钥,而差异化功率分析则有助于防止侧信道攻击。器件包含永久性篡改惩罚,以进一步防止误用。最大限度延长正常运行时间,增强的单事件干扰性能有助于客户进行快速、安全配置,并提升可靠性。

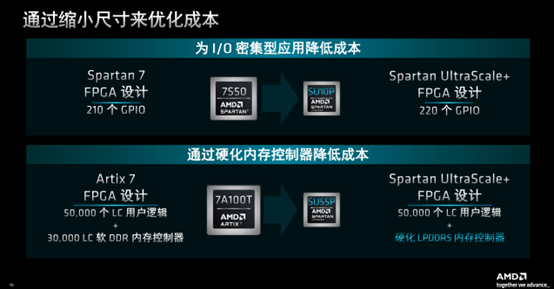

客户如何通过Spartan UltraScale+ FPGA系列做设计来节约成本呢?AMD 自适应和嵌入式计算事业部FPGA成本优化型产品组合产品线经理Romisaa Samhoud以图2为例进行了说明,如果是200以上I/O小的密度的器件,使用现行的Spartan 7S50产品(28纳米器件)是用200个I/O,如果换成Spartan UltraScale+ FPGA系列更小的设备,同样数量的I/O,它可以实现成本的节约。同时这个设计可以在同样的I/O数量但是更小的器件上来进行,也就是SU10P。如果客户的设计采用软DDR内存控制器,3万个逻辑单元,还有5万个逻辑单元的用户逻辑,可以看到它可以放到7A100T里,在Spartan UltraScale+ FPGA系列我们还有硬化IP,客户的设计可以完全放在SU55P这样的规格上节约整个架构的空间及成本。

图2

在软件开发工具方面,AMD FPGA 和自适应 SoC 全产品组合由 AMD Vivado 设计套件和 Vitis 统一软件平台提供支持,帮助开发人员提高他们工作效能的最好办法就是只需要学会用一套工具就能够保持高效的工作效能。AMD的软件工具使硬件与软件设计人员能够通过一款设计人员环境进行从设计到验证,充分利用这些工具及所包含 IP 的生产力优势。

评论