nepes采用西门子EDA先进设计流程,扩展3D封装能力

西门子数字化工业软件日前宣布,韩国nepes公司已采用西门子ED 的系列解决方案,以应对与3D封装有关的热、机械和其他设计挑战。

本文引用地址:http://www.amcfsurvey.com/article/202403/456283.htmSAPEON韩国研发中心副总裁Brad Seo表示:“nepes 致力于为客户提供全面的半导体封装设计和制造服务解决方案,帮助客户在半导体市场上获得持续成功。今天的半导体行业对于性能和小尺寸的需求越来越高,nepes与西门子EDA的携手将帮助我们实现发展所需的创新技术。”

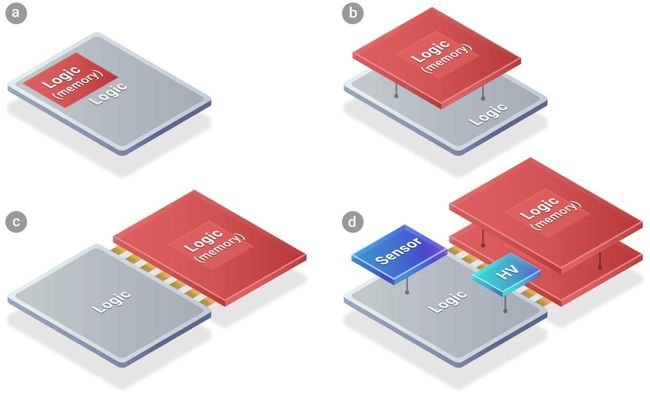

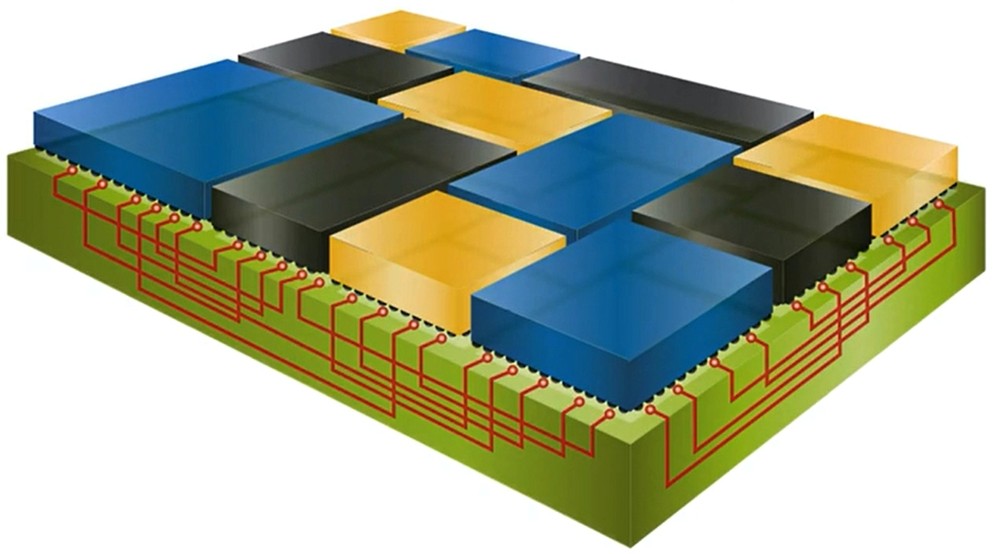

nepes 是外包半导体封装测试服务(OSAT)的全球领导者,致力于为全球电子业客户提供世界级的封装、测试和半导体组装服务;nepes 还同时提供封装设计服务,包括晶圆级封装、扇形晶圆级封装和面板级封装。

基于已有技术,nepes加入西门子EDA的 Calibre® 3DSTACK、用于电气规则检查的HyperLynx™,以及 Xedition™ Substrate Integrator和Xpedition™ Package Designer一系列技术能力,推动封装技术创新,为全球IC客户提供快速可靠的设计服务,包括基于2.5D/3D的chiplet设计。

西门子数字化工业软件电路板系统高级副总裁AJ Incorvaia表示:“西门子EDA致力于向nepes等供应链合作伙伴提供行业领先的半导体封装技术,助其实现数字化目标。西门子EDA与nepes建有良好的合作关系,此次双方进一步合作将为共同客户带来更多优选的解决方案。”

评论