高速面阵CCD KAI-01050功率驱动电路的设计方案(一)

2.1 电压偏置模块

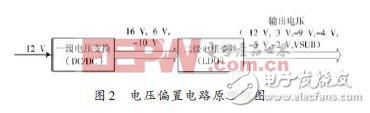

功率驱动电路所需电压如表1所示,根据电压需求设计的电压偏置电路原理框图如图2所示。

系统采用+12 V电源供电,电压偏置电路首先使用开关电源芯片(DC/DC)进行一级电压转换。又由于DC/DC输出电压的纹波和开关噪声较大,不能直接给电路供电,所以使用LDO芯片进行二次电压变换,最终获得稳定、低噪声的电压。

2.2 水平转移和复位驱动电路

由以上可知,欲使CCD工作在最高帧频120 f/s,水平转移和复位时钟的频率需要工作在40 MHz.每个驱动信号功率需求如式(1)所示:

式中:C 为CCD时钟管脚的等效电容;V 为信号的摆幅;f 为工作频率。由式(1)可知,频率越高,需要的功率越大。

时钟信号不仅对高低电平电压有要求,上升沿和下降沿时间也必须要在指定的范围内。要得到指定的上升时间,就必须提供相应大小的驱动电流。对CCD 功率驱动电路的要求是在较大电压摆幅情况下在快速的变化沿时能够提供足够大的瞬态驱动电流。

由于CCD 为容性负载,由下面电容模型的公式可以算出驱动器需要提供的瞬态电流。

上面的计算中定义上升或下降沿的时间对应电平幅度的10%~90%.设边沿变化为线性的,对于水平转移时钟,电压幅度为4 V,负载电容取最大值90 pF,对于40 MHz 信号,上升或下降沿的最长时间按5 ns 计算,那么在边沿变化处会产生的电流为57.6 mA;对于复位时钟,电压幅度为5 V,负载电容取最大值16 pF,对于40 MHz复位信号,占空比取1∶4,上升或下降沿的时间按3 ns计算,那么在边沿变化处会产生的电流为21.3 mA.

本文选用Intersil公司高速驱动器ISL55110和二极管钳位电路进行复位和水平转移时钟的驱动电路。此驱动器最高可提供3.5 A的驱动电流,在100 pF的负载电容下,电压摆幅为12 V时,上升时间仅为1.4 ns,下降时间仅为1.2 ns.完全满足水平转移和复位时钟的功率驱动要求。

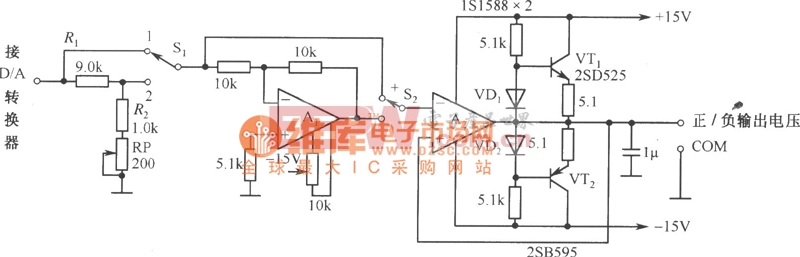

2.3 垂直转移驱动电路

垂直转移信号分为两种:

(1)正常的两电平阶梯波形的V2T,V2B,V3T,V3B,V4T和V4B,高电平为GND,低电平为-9 V;

(2)三电平阶梯波形的V1T 和V1B,高电平为12 V,中间电平为GND,低电平

评论