从4004到core i7:处理器的进化史 (3)-3-真正的CPU

上一个帖子中我把4004作为所有后续的性能越来越高的处理器的鼻祖。在这个贴之中我们来讨论CPU进化史中的第一个里程碑:80286处理器。

本文引用地址:http://www.amcfsurvey.com/article/233546.htm从4004到8008再到8080甚至是8086,CPU的进化在逐渐进行着。晶体管数量翻了几番,主频翻了几番,但是内部的结构的变化还不足以引起我们的兴趣为之单独写一个帖子。

这一切在80286都发生了彻底的改变。

当CPU的功能变得越来越强大,速度变得越来越快的时候,人们渐渐地不满足于让它只做一件事情,比如说IBM Displaywriter,而想要让它具有完成多个任务的能力。

多个任务意味着不同功能的多段程序,这样多的程序不大可能由intel一家或者末端用户自己全部写出来。也就是说,我们的CPU可能出现很多不同的程序提供者。

一个很自然的想法就是,这么多程序员中间必然有很多不靠谱的(别忘了,当时汇编都是个新鲜玩意呢),以及很多靠谱但心怀不轨的。要想让CPU正常有序地运行多段程序,没有某种管理机制看来是行不通的。

于是乎思路就很明显了,程序要按照受信任的程度分成三六九等。不靠谱的、心怀叵测的程序不受信任,虽然可以在占据CPU的这一小段时间里肆虐,却不应该危害到其他程序,更不应该危害到监察者的安全。

对于一段程序来说,能干的坏事无非就是更改一下其他程序的状态,也就是内存里的数据,或者是执行一段来路不明的代码。如果能禁止这两者的发生那么基本上就不会闹出什么大乱子出来。

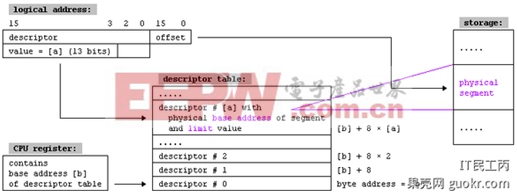

有了上面这个思路,再看一看下面intel的实现就显得很自然了:

在上图中,连续的物理内存被分成了很多个段(segment),内存单元的逻辑地址采用段基址+偏移的方式描述。,每个段有自己的访问权限,每个程序都有一个从3~0的权限界别(这4个级别一直被沿用至今天)。如果当前这段程序想要访问某一个内存,或者想执行某一段代码,就必须经受硬件完成的权限检查,只有当权限高于等于想要访问内存的权限时才允许访问,否则就会抛出错误。关于硬件错误的抛出、处理后面还要再提,这里我就不讲了。

由于这种权限制度保护了内存免受其恶意或不靠谱程序的侵害,因此这种状态被称为CPU的保护模式。今天的几乎所有桌面级别和以上的处理器都运行在保护模式下。上面提到的3~0的权限级别的划分也为后来的操作系统(operating system)奠定了基础。

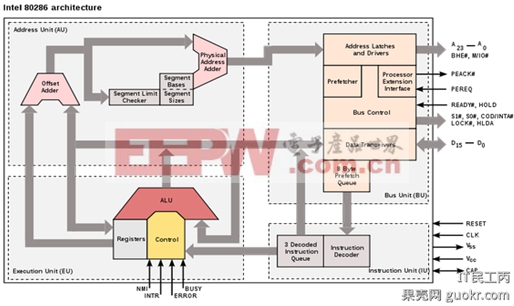

80286的另一个进步(实际上是8086相对于之前的进步)可以在下面这张图中看出来

左上方的address unit就是上面讲到的分段机制对应的硬件。它的工作就是查映射表由逻辑地址得到实际的物理地址,并且进行权限检查。右上方的bus unit中我们感兴趣的部分是最下面的8 byteprefetch queue和下方的instruction unit。

在左下方的execution unit以及左上方的address unit在执行某一个指令的同时,右下方的instruction unit在解码后面的若干条指令。

对比前面的4004,我们发现286并不是等待一条指令完全执行完毕之后才开始执行下一条的。相反地,在286内部可能有若干条指令处于不同的状态:一条正在被ALU等部件实际执行,其余的可能已经完成了取指正在等待译码,或者译码都完成了就是等着执行了。毫无疑问,比起4004的执行效率提高了不少。

这种将整个CPU划分为2个模块,每个模块在同一时间执行不同任务的思想正是流水线(pipeline)(想想汽车装配的流水线吧)。尽管286时可能还没有这个概念,但无疑已经实现了最初的雏形。后面我们将要看到,流水线是我们为数不多的优化处理器性能的主流方法之一。

晶体管相关文章:晶体管工作原理

晶体管相关文章:晶体管原理

评论