一种基于FPGA的流水线FIR滤波器设计

摘要:有限冲击响应(FIR)滤波器是数字通信系统中常用的基本模块。文章设计了一种流水结构的FIR滤波器,通过FPGA对其进行硬什加速控制。仿真结果验证了所设计的FIR流水结构滤波器功能的正确性。

本文引用地址:http://www.amcfsurvey.com/article/256427.htm0 引言

随着数字通信技术的快速发展,高质量的信息处理对滤波器的性能和资源占有量提出了更高的要求。有限冲击响应(FIR)数字有限冲激响应滤波器在语音、谱分析等数字信号处理领域有着广泛的应用,是信号处理系统中重要的组成部分,其性能往往对整个系统的性能和功耗产生至关重要的影响。因此,如何最大程度地优化FIR滤波器的性能成了电路实现中需要特别关注的问题。

现代应用程序的核心计算函数一般通过软件编程在处理机上执行,处理速度慢,当核心函数较复杂时,需要较长处理时间,采用硬件处理,能够减少处理器占用时间,提高处理器的利用率,从而提高系统的性能。现代数字系统中广泛使用现场可编程逻辑器件(FPGA)作为实现平台,本文提出一种基于FPGA的FIR滤波器设计,充分利用硬件电路固有的快速特性,替代传统的软件算法,减少占用处理机的资源,提高了FIR滤波器的性能。

1 FIR滤波器流水结构设计

FIR滤波器具有有限冲击响应系统稳定收敛、线性相位的优越特性,不会产生相位失真。FIR数字滤波器有直接型结构和转置型结构(如图1所示)等多种实现结构,为提高电路的执行效率、简化电路,本文采用分布式算法结构或者转置结构的FIR滤波器加以实现。与基本结构FIR滤波器不同,采样数据同时进入乘法器,先计算乘积和,再进行延迟,通过流水线的加法器链将乘积结果流水相加,最终得到滤波输出,优化后其硬件逻辑基本单元结构如图2所示。

设FIR滤波器单位脉冲响应h(n)长度为N,其输入序列和输出序列的差分方程为:

其中,ωp为归一化通带截止角频率,ωs为归一化阻带截止角频率,δp为峰值通带纹波,δs为峰值阻带纹波。由于FIR滤波器阶数N必须为整数,以N=8为例,可得到FIR滤波器的系数h(n)。如表1所示。

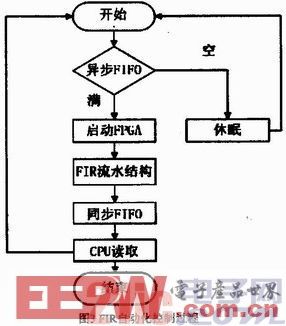

2 FPGA自动控制设计

FIR自动化控制过程见图3所示。为了解决内外时钟不同速率问题,采用异步FIFO作为缓冲的存储器。当外部数据开始进入时,数据依次进入异步FIFO;当异步FIFO状态为满时,则FPGA开始工作,控制异步FIFO中的数据依次进入FIR流水结构进行运算,并将计算结果依次按顺序输出至后级同步FIFO中,等待CPU进行读取工作。整个数据处理过程主要由异步FIFO深度进行控制,当其状态为空且前一帧数据处理完全结束后,整个系统将保持现有状态,进入休眠过程,等待下一个数据的进入才开始唤醒工作。

3 实验结果及分析

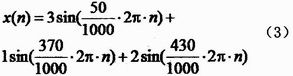

利用Matlab进行仿真,假定输入序列采样为

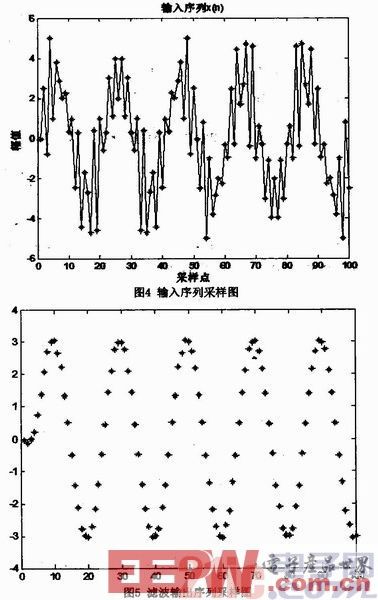

即50Hz、370HZ、430Hz信号的混合信号,其中n=1,2,3…100。设计N=8的低通FIR滤波器,截止频率为100HZ。图4为输入序列,图5为输出滤波结果。

用Modelsim进行逻辑仿真,FPGA控制信号时序如图6所示。

FIR流水线结构运算输出及运算结果FIFO存储过程仿真图如图7所示。

图中为FIR流水结构中各级寄存器状态仿真图,将其提取,并建立仿真表如表2所示。

将FIR输出序列逻辑值与仿真结果通过表2比较可知,仿真运算结果一致。综合上述一系列仿真图与仿真表可知,FIR流水结构功能正确,实现了FPGA控制的FIR滤波器设计。

4 结论

本文设计了一种基于FPGA的硬件加速器,实现了大量减少逻辑运算单元的流水线的运算方式,并通过Matlab与Modelsim的仿真,验证了所设计的FIR流水结构滤波器功能的正确性。

滤波器相关文章:滤波器原理

fpga相关文章:fpga是什么

滤波器相关文章:滤波器原理

电源滤波器相关文章:电源滤波器原理

数字滤波器相关文章:数字滤波器原理 燃气报警器相关文章:燃气报警器原理

评论