数字电源UCD92xx的输出电压波形优化与分析

基于UCD92xx与UCD7xxx的非隔离数字电源,其输出电压在软启动阶段经常出现“台阶”现象,波形不平滑,尤其是输出电压设定为较低值时,如1.0V。这种“台阶”现象与UCD92xx 软启动的设计原理有关,但完全可以通过一定的措施来优化并最终解决。本文从UCD92xx的环路和最小占空比宽度两个方向进行优化与分析,最终取得了理想的效果。

1、软启动原理及待优化输出电压波形

数字电源UCD92xx的软启动是通过对参考电压以步进方式增加来实现的,整个过程是由芯片内部的软件自动完成的。在一款基于UCD9224和UCD74120的单板上测试时发现,其输出电压波形在软启动阶段有明显的“台阶”现象,波形不平滑。

1.1 数字电源软启动原理介绍

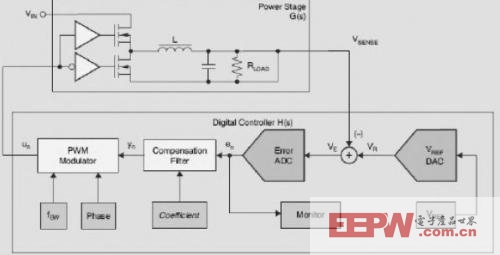

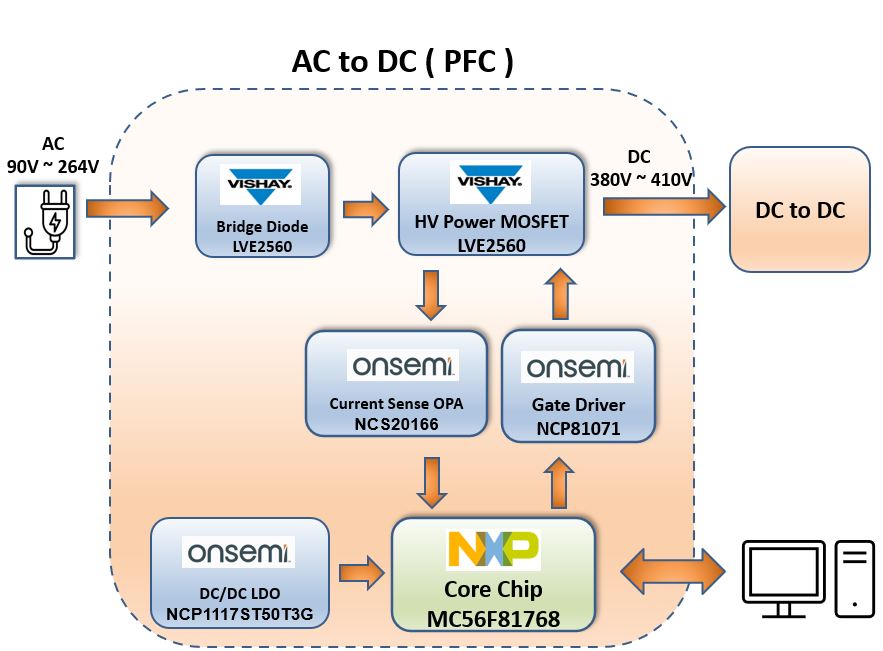

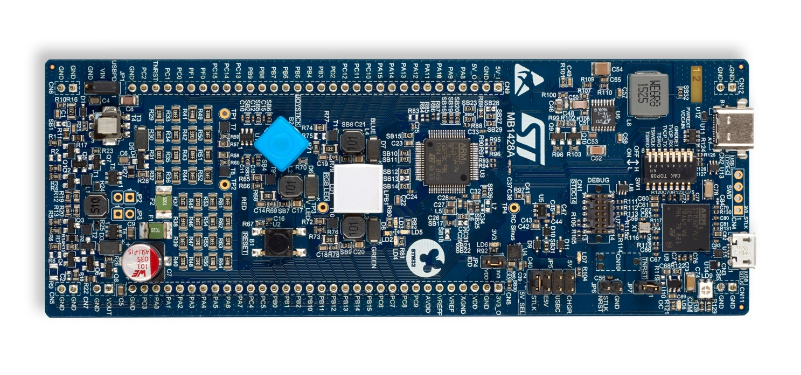

图1所示的是数字电源UCD92xx的功率支路和控制支路。控制支路主要集成在UCD92xx芯片内部,包含误差生成及模数转换,环路补偿,PWM计算及产生等。其中,参考电压(VREF)电压的设置亦包含在控制支路。

依据软件算法,在软启动阶段,VREF每100μs增加一次,直至软启动完成,即输出电压达到最终的设定值。例如,输出电压设定为1.0V,软启动的时间设置为4ms,则在软启动阶段输出电压每一次增加25mv,直至达到1.0V。

图1:数字电源功率级和控制级框图

1.2 待优化的输出电压波形

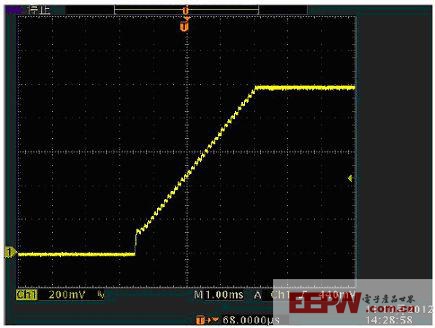

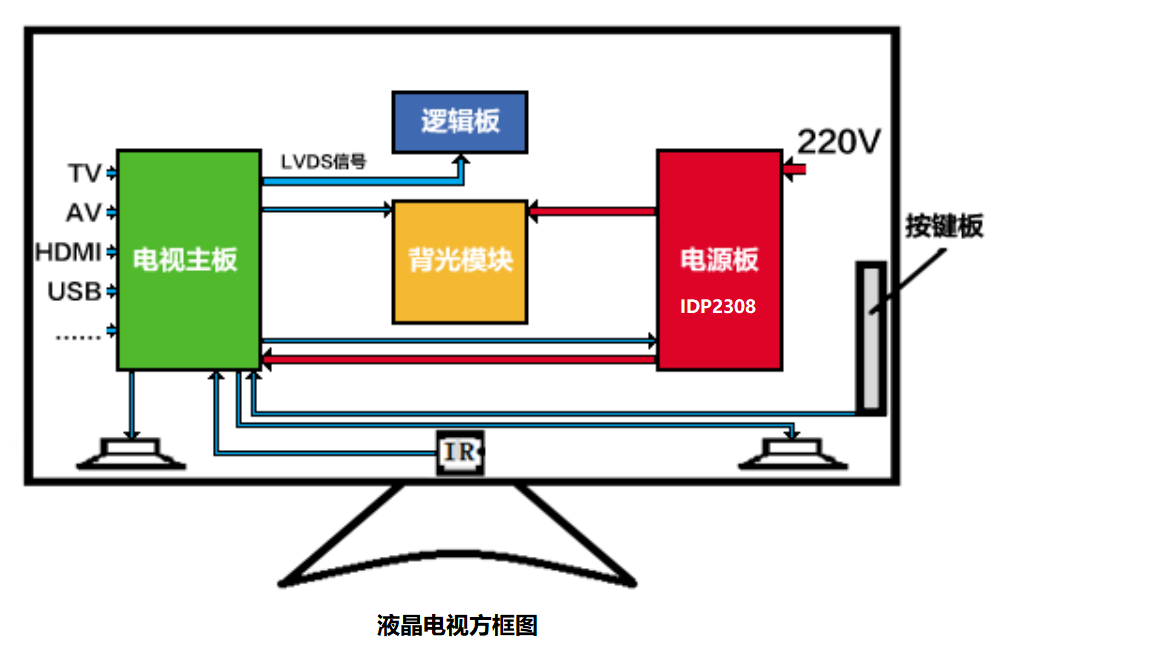

图2所示的是输出电压波形,可以观察到在软启动阶段输出电压的波形不够平滑,有明显的“台阶”现象。

该波形是在一款基于UCD9224和UCD74120的参考版上测得。主要测试条件为:测试环境常温,输入电压为12V,输出电压为1.0V,输出端带载20A。另外,测试时,数字环路的详细配置见下文2.4节。

图2:输出电压波形

1.3输出电压“台阶”现象的初步分析

图3所示的是时间轴展开后观察到的输出电压波形。通过测量可知,每经过100μs输出电压增加一次,增加的幅度大约为23mV,与理论计算值25mV基本一致。

同时也可以观察到,输出电压的每一次增加都是很快的完成,而不是缓慢增加。从功率级支路上分析,这是由于占空比快速增加造成。从控制级支路分析,则原因可以初步归结为环路过快造成的。

图3:输出电压的步进幅度

2 数字电源模拟前端及环路

数字电源控制环路包含了模拟前端,数字环路补偿等模块,在配置环路时需要综合考虑。其中,数字环路还包含非线性增益模块,使能后可以有效提升整个电源的动态响应性能。

2.1 数字电源模拟前端(AFE)

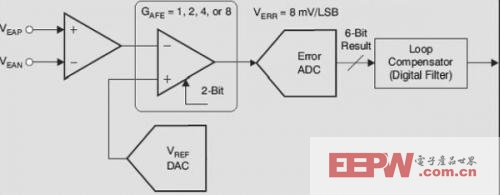

图4红色框内电路为数字电源模拟前端(Analog-Front End,AFE)的一部分,其增益可以设置为1,2,4,8等四个不同的值。设置不同的增益,则ADC的输出精度也随之不同,比如设置增益为4,则输出精度为2mV;设置增益为1,则输出精度为8mV。

在相同输入误差(VEAP-VEAN)的情况下,不同的AFE 增益值将直接影响环路指标。其影响趋势为,增益越大,环路带宽越宽。

图4:数字电源的模拟前端

评论