基于NiosⅡ的1553B总线通讯模块设计与开发

自2005年9月LXI总线推出以来,已经显示出其组建测试系统的众多优点。基于LXI总线组建测试系统具有易于使用、灵活性高、模块化和可扩缩性、实现更快的系统吞吐率、可分布式应用、长寿命、低成本、通过IEEE1588时钟同步、机架空间小、合成仪器等诸多优点。

本文引用地址:http://www.amcfsurvey.com/article/268250.htm1553B总线的全名为“时分制指令/响应式多路传输数据总线”,国内多型战斗机、军舰等武器平台都采用其作为传输总线。因此研制基于LXI总线的1553B通讯模块,不仅能满足多型武器装备对1553B总线的测试需求,也对LXI总线在国内的研究和应用有推动作用。

1 模块总体方案

模块基本设计指标为:满足LXI规范C类仪器标准;支持DHCP、自动配置IP地址和手动配置IP地址;支持ICMP协议、TCP/IP协议和UDP协议;同步采用网络命令方式;能完成1553B在BC模式下的所有功能。

根据指标要求采用基于SOPC的32位处理器+实时多任务操作系统(Real Time Operation System,RTOS)总体方案,在一块FPGA芯片上集成了控制器和逻辑单元,既降低了开发的难度、减少了模块体积,也易于以后的升级。32位处理器有足够的资源可以扩充利用,RAM和ROM可以做的足够大,整个TCP/IP协议族可以做到系统里面去,甚至可以嵌入一个带TCP/IP协议族的操作系统。

2 基于SOPC的硬件设计与开发

片上可编程系统(System on a Programmable Chip,SOPC)将处理器、存储器、I/O口、LVDS和CDR等系统设计需要的功能模块集成到一个PLD器件上构建成一个可编程的片上系统,是一种灵活高效的SOC解决方案。SOPC结合了SOC和可编程逻辑器件各自的优点,具有灵活的设计方式、可剪裁、可扩充、可升级,并具备软硬件在系统可编程的功能,成为SOC设计的新趋势。

2.1 模块硬件架构

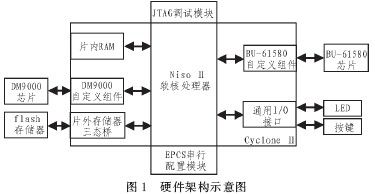

模块硬件主要由NiosII软核处理器、以太网组件、1553B总线组件、存储器、片内RAM、通用I/O接口和调试配置模块7部分组成,架构示意如图1所示。

1)NiosII软核处理器:模块的CPU,负责系统工作调度。在其内部移植了μC/OSII实时操作系统和LwIP协议;它接受客户端通过以太网发送过来的请求,经解析后回复Web界面或控制1553B功能接口;2)以太网组件(DM9000A):完成对以太网控制器的操作,将网络上的数据经以太网控制器送到网际层,由NioslI软核处理器内的LwIP协议处理;或者将网际层送来的数据经以太网接口发送出去:3)1553B总线组件(BU-61580):受NiosllI软核处理器控制,完成在BC模式下各类消息和命令的发送及状态的读取;4)Flash存储器:主要用来存储模块的一些固定参数和静态Web界面;5)片内RAM:RAM是在FPGA剩余逻辑中用Quartusll内所带的MegaWizard管理器生成的,这样就不需要外加RAM芯片。片内RAM主要是用来存储程序运行过程中所接收和产生的一些数据;6)通用I/O接口:用来完成对LED或按键的控制;7)JTAG调试模块和EPCS配置模块:J1TAG模块用来完成对程序的调试工作。配置是对FPGA的内容进行编程的过程,每次上电后都需要配置,EPCS配置模块允许NioslI访问EPCS串行配置器件。

具体开发主要有3部分工作:1)NiosII软核处理器及其外设的设计。2)自定义宏功能模块RAM的开发,这部分工作在QuartuslI软件中完成;3)应用软件程序的编写,在NiosIIIDE软件开发环境中完成。

2.2 模块硬件设计

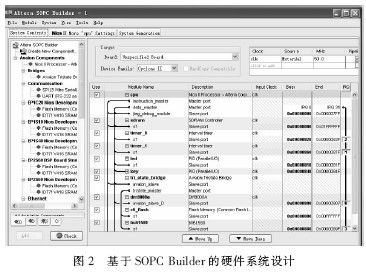

SOPC Builder是Altera公司为用户自定义系统而开发的工具。用户使用SOPC Builder可以将IP核、存储器、接口、微处理器和自定义组件等复杂系统组件简单又快速的集成到Ahera高密度FPGA芯片上。按照模块硬件系统的要求,借助SOPC Builder生成的模块硬件结构,包括:32位标准NiosII软核处理器:cpu;JTAG调试接口:jtag-debug-module;外部SDRAM存储器接口:sdram;Avalon三态桥:tri_state_brid ge;EPCS串行闪存控制器:EPCS_controller;外部FLASH存储器接口:cfi_flash;定时/计数器:time0/timel;以太网接口:dm9000a;1553B接口:bu61580;LED接口:led;64KRAM接口:RAM;按键接口:key;系统识别模块:sysid。

2.3 宏功能模块RAM生成

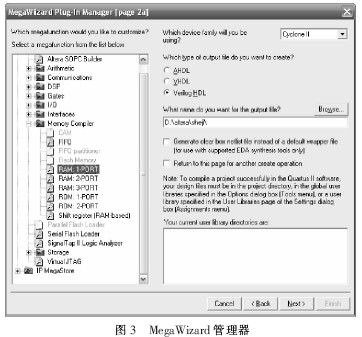

CycloneII器件内部的RAM块只有M4K一种,可用来实现真正的双端口、简单双端口和单端口的RAM,可以支持移位寄存器和ROM方式。用QuartusII内所带的MegaWizard管理器来生成RAM,首先运行MegaWizard管理器选择“创建一个新的宏功能”,在出现的对话框内选择Insta lled Plug-Ins下的memory compiler下的RAM:1-PORT,如图3所示。

在接下来的各页中选择如下参数:数据线宽度16位;存储64个字;自动单时钟驱动;选择生成*.v,*.bsf,*_inst.v,*_bb.v,*_waveforms.html 5个文件。其他参数默认即可。

tcp/ip相关文章:tcp/ip是什么

通信相关文章:通信原理

存储器相关文章:存储器原理

评论