深入研究DDR电源(07-100)

我们将深入研究需要这些电压的原因。

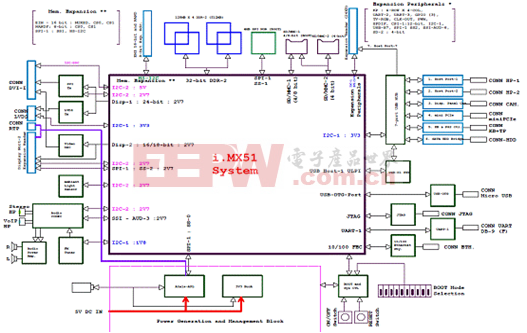

本文引用地址:http://www.amcfsurvey.com/article/81733.htm尽管DDR存储器在无需加倍时钟频率的情况下使数据传输率加倍,避免了PC板设计和布局的复杂性,但它要求有更严格的dc稳压、更高的电流和对端电源电压(VTT)和存储总线电压(VDD)紧密的跟踪。新型串联端接逻辑(SSTL)拓朴的引入是用于提高抗噪性、增加电源抑制并使用更低的电源电压以降低功耗。

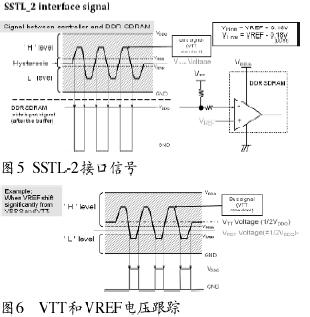

JEDEC标准JESD8-9A(用于SSTL_2)和JESD8-15(用于SSTL_18)定义了VDDQ、VTT和VERF以及驱动器/接收器规格以分别满足在VDDQ= 2.5 V (用于 DDR1) 和VDDQ = 1.8 V (用于 DDR2)时的噪声容限。下面,我们看看这种接口以更好的理解VREF和VTT的需要。

SSTL接口

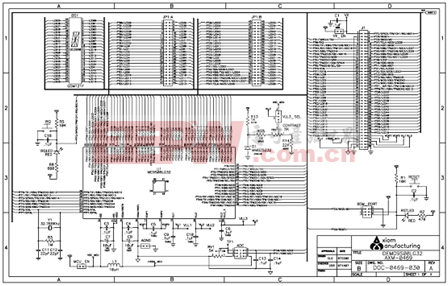

图3显示了DDR存储器的新型串联端接逻辑(SSTL)拓朴。

SSTL_2的接口具有下述特性:

·DDR存储器具有推挽式的输出缓冲,而输入接收器是一个差分级,要求一个参考偏压中点,VREF。因此,它需要一个能够提供电流和吸收电流的输入电压端。

·在驱动芯片集的任何输出缓冲器和存储器模块上相应的输入接收器之间,我们必须端接一个布线跟踪或带有电阻器的插头。

VTT电源的电流流向随着总线状态的变化而变化。因此,VTT电源需要提供电流和吸收电流 (source & sink),如图4中红色和蓝色箭头所示。

由于VTT电源必须在 1/2 VDDQ提供和吸收电流,因此如果没有通过分流来允许电源吸收电流,那么就不能使用一个标准的开关电源。而且,由于连接到VTT的每条数据线都有较低的阻抗,因而电源就必须非常稳定。在这个电源中的任何噪声都会直接进入数据线。

图5详细阐述了信号如何流过SSTL_2接口。

存储器相关文章:存储器原理

评论