基于SystemC的系统级芯片设计方法研究

随着集成电路制造技术的迅速发展,SOC设计已经成为当今集成电路设计的发展方向。SO C设计的复杂性对集成电路设计的各个层次,特别是对系统级芯片设计层次,带来了新挑战,原有的HDL难以满足新的设计要求。

本文引用地址:http://www.amcfsurvey.com/article/83115.htm硬件设计领域有2种主要的设计语言:VHDL和Verilog HDL。而两种语言的标准不统一,导致软硬件设计工程师之间工作交流出现障碍,工作效率较低。因此,集成电路设计界一直在寻找一种能同时实现较高层次的软件和硬件描述的系统级设计语言。Synopsys公司与Coware公司针对各方对系统级设计语言的需求,合作开发了SystemC,他可以较好地实现软硬件的协同设计,是系统级芯片设计语言的发展趋势[1]。

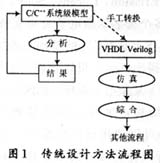

1 传统的系统级设计方法[1]

在传统设计方法中,设计的系统级往往使用UML,SDL,C,C++等进行描述以实现各功能模块的算法,而在寄存器传输级使用硬件描述语言进行描述。最广泛使用的2种硬件描述语言是VHDL和Verilog HDL,传统的系统设计方法流程如图1所示。从图中不难看出,传统的设计方法会出现如下弊端:

首先,设计人员需要使用C/C++语言来建立系统级模型,并验证模型的正确性,在设计细化阶段,原始的C和C++描述必须手工转换为使用VHDL或Verilog HDL。在这个转换过程中会花费大量的时间,并产生一些错误。

其次,当使用C语言描述的模块转换成HDL描述的模块之后,后者将会成为今后设计的焦点,而设计人员花费大量时间建立起来的C模型将再没有什么用处。

再次,需要使用多个测试平台。因为在系统级建立起来的针对C语言描述的模块测试平台无法直接转换成针对HDL语言描述的模块所需要的测试平台。

2 使用SystemC的必要性

无论采用什么样的设计方法学,人们都需要对SOC时代的复杂电子系统进行描述,以选择合 适的系统架构,进行软硬件划分,算法仿真等等。描述的级别越低,细节问题就越突出,对实际系统的模仿就越精确,完成建模消耗的时间、仿真和验证时间就越长。相反,描述的抽象级别越高,完成建模需要的时间就越短,但对目标系统的描述也就越不精确。作为设计人员必须在速度和精确性之间做出选择。

人们对系统级描述语言的要求是:高仿真速度以及建模效率、时序和行为可以分开建模、支持基于接口的设计、支持软硬件混合建模、支持从系统级到门级的无缝过渡、支持系统级调试和系统性能分析等。人们迫切需要一种语言单一地完成全部设计。这种语言必须能够用于描述各种不同的抽象级别(如系统级、寄存器传输级等),能够胜任软硬件的协同设计和验证,并且仿真速度要快。这就是所谓的系统级描述语言SLDL,而传统的硬件描述语言如VHDL和Verilog HDL都不能满足这些要求。

SystemC就是目前这方面研究的最新、最好的成果,他扩展传统的软件语言C和C++并使他们支持硬件描述,所以可以很好地实现软硬件的协同设计,是系统级芯片设计语言的发展趋势。

3 SystemC简介

1999年9月,微电子业内的一些一流的EDA公司、IP提供商、半导体制造商及系统和内嵌式软件设计公司联合创建了开放SystemC创始会组织(Open SystemC Intitiative,OSCI),并推出了基于C++的系统级设计语言SystemC。OSCI是一个非盈利性组织,他负责维护和发展SystemC。SystemC是完全免费的,这使得EDA供应商能够充分自由地了解SystemC库的源代码以优化他们的各种解释工具;包括Synopsys,Cadence,Frontier Design,ARM,Eri ssion,Lucent,Sony,TI等核心成员。目前已经有50多个著名的微电子公司支持该标准[2]。

SystemC本质上是在C++的基础上添加的硬件扩展库和仿真核,这使得SystemC可以建模不同抽象级别的(包括软件和硬件的)复杂电子系统。他既可以描述纯功能模型和系统体系结构,也可以描述软硬件的具体实现。SystemC源代码可以使用任何标准C++编译环境进行编译,生成可执行文件;可以使用综合工具(如Synopsys SystemC Compiler)将SystemC的寄存器传输级描述综合为Verilog HDL或者VHDL的代码用于FPGA设计,也可以综合为EDIF网表用于A SIC设计[3]。

SystemC具有所有硬件描述语言所共有的基本特征,包括模块、进程、端口和信号等。不同的是,在SystemC中时钟被单独定义为一个特殊的信号,这大大简化了时钟信号的定义,SystemC还支持具有任意相位关系的多个时钟。在SystemC中使用了sc_set_tim e_resoluti on()和sc_set_default_time_unit()来定义时间分辨率和时间单位,这与Ve rilog HDL的timescale语法在功能上是等效的。

pic相关文章:pic是什么

c语言相关文章:c语言教程

c++相关文章:c++教程

评论