基于NiosII的多通道PWM信号测量/产生器节点设计

摘要:针对于列车控制系统半实物仿真平台测速测距模块的多通道PWM信号测量/产生的要求,提出了一种利用NiosII软核处理器替代通讯用MCU的智能多通道PWM信号测量/产生器的设计方案。

关键词:NiosII;PWM;FPGA;SOPC

2008年4月28日收到本文。

引言

列车控制系统半实物仿真平台是基于HLA规范,将各种铁路通信信号系统内的设备通过建模或实物连接到一起,构建成的一个完整的列车运行控制仿真平台,用以进行系统研究、系统仿真及新系统的开发。

实物测控接口平台是列车控制系统半实物仿真平台的重要组成部分,是实物设备和HLA仿真环境的接口,实现实物系统和仿真环境之间的信息交互,保证其协同并行工作。接口平台使用了嵌入式Linux的架构以提供HLA界面,同时提供和实物设备对应的物理信号接口,其中包括车载实物系统中的测速测距模块需要的多路PWM信号测量/产生器节点。

常用的MCU或者PWM芯片最多能提供16路PWM信号输出通道,如果用MCU来实现PWM信号周期和占空比的测量,需要占用大量的硬件资源并且效率不高,因此使用MCU实现较多通道的PWM信号测量/产生器对MCU的处理能力要求较高,成本较高。若采用MCU/DSP作为外界通讯接口,使用FPGA实现多通道PWM信号测量/产生器,可以完成设计目标,但是系统复杂度较高。本文提出了一种利用NiosII软核处理器替代通讯用MCU的智能多通道PWM信号测量/产生器的设计方案。该设计仅使用单片FPGA构建SOPC,系统复杂度低,可靠度高。

节点硬件设计

Nios II是一款基于哈佛结构的32位RISC 处理器,包括3 种内核。

智能PWM节点设计的核心在于NiosII软核处理器的配置和利用FPGA实现多通道PWM信号测量/产生器。

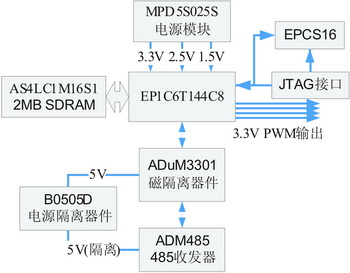

节点硬件方框图如图1所示,FPGA选择了Altera公司低成本FPGA Cyclone EP1C6Q240C8,电源模块选择了Murata公司的可提供3路1.0~3.6V可调输出的MPD5S025S,直接提供FPGA需要的3.3V,2.5V和1.5V电源;NiosII的程序代码保存在FPGA的配置芯片中,配置芯片选择了16Mbit串行EPCS16,足够保存NiosII应用程序;外扩2MByte SDRAM芯片AS4LC1M16S1;通讯接口为RS-485,采用磁隔离的方式,使用的隔离器件是ADuM3301磁隔离芯片,由一个5V/5V的DC/DC电源隔离器件B0505D提供隔离端的电源。FPGA输入/输出的多通道PWM信号通过接插件连出。整个节点设计非常简洁,可以做到很小的体积。

图1 智能PWM节点硬件方框图

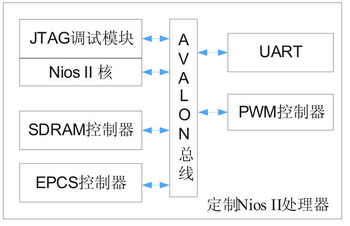

Nios II软核处理器配置

NiosII软核处理器使用Quartus II集成的SOPC Builder进行配置,配置图如图2。根据节点设计的需要,使用Nios II/s为处理器核心,UART为通讯接口,添加SDRAM控制器和EPCS控制器。使用32bit+12bit PIO作为PWM控制器,这个控制器是基于总线方式的控制器与FPGA内的PWM信号测量/产生器相连读取/写入周期和占空比信息,具体定义为:32bit数据,8bit通道地址,1bit读/写,1bit配置允许和1bit配置测量/产生,这2bit可以配置对应地址PWM通道为测量或产生,1bit预留。使用这种总线方式控制器配置PWM通道信息的速度快并且易于编程。

图2 智能PWM节点NiosII处理器配置图

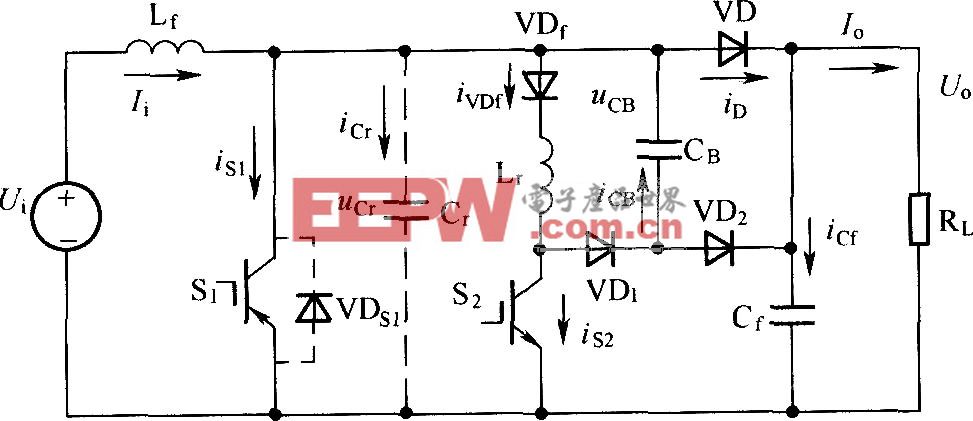

FPGA内多通道PWM信号测量/产生器模块

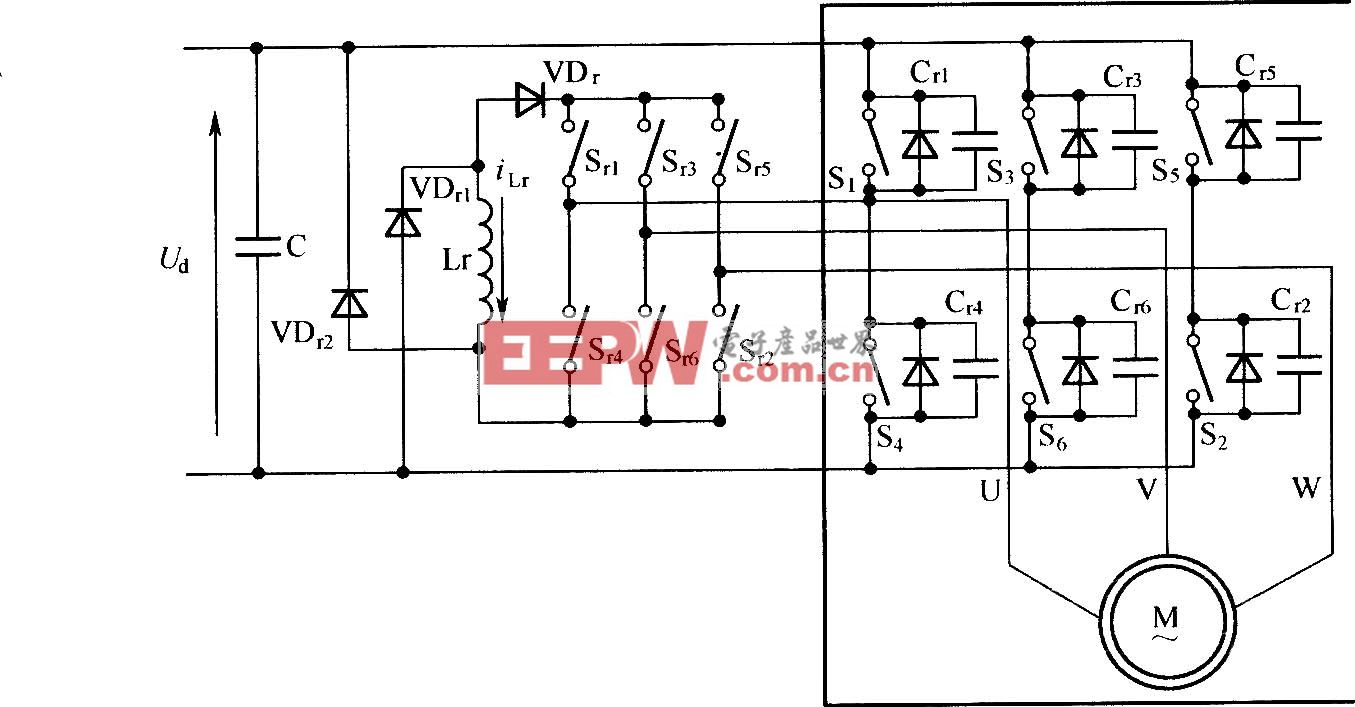

多通道PWM信号测量/产生器模块FPGA功能框图如图3所示。用FPGA实现PWM信号的产生和测量的核心就是计数器的使用,每个通道的PWM需要8个计数器,其中4个是PWM信号产生用的预置高电平计数器,预置低电平计数器,高电平计数器和低电平计数器;其余4个是PWM信号测量用的高电平计数器和低电平计数器以及对应的最大值寄存器,由于资源的限制,这些计数器必须用RAM实现。

图3 多通道PWM信号测量/产生器模块FPGA功能框图

pwm相关文章:pwm原理

评论