定宽截断式并行乘法器的实现研究

1、乘法器的介绍

乘法器是多媒体芯片和DSP芯片中的核心部件之一,它决定着芯片的性能表现和面积大小。为了提高处理速度,并行乘法器通常需要增加面积和架构上的复杂度来实现。过去,有很多的学者提出不同的乘法器架构来减小芯片的面积和提高乘法运算的速度。本文所提出的定宽截断式并行乘法器架构,可大大减小乘法器的面积,对乘法器的整体性能却无太大影响。这种乘法器主要应用于多媒体和DSP芯片的定宽乘法操作中。

2、截断乘法器的设计实现

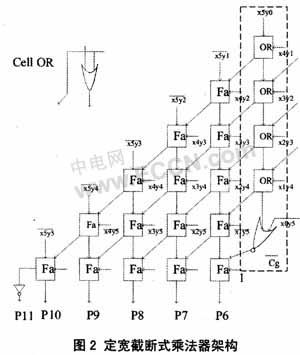

定宽乘法器可以直接由传统的并行乘法器截去一半的半加器运算单元得到,但在运算结果中会产生巨大的误差,这在多媒体和DSP芯片定宽乘法操作的数据处理作中是不愿看到的。Kidambi et al.给出一种简单的减小误差的方法,它把保留下来的运算单元给定一个恒定的误差补偿。然而,这样产生的结果误差仍然会很大。在设计中,通过有效的进位产生电路对剩下的运算单元进位补偿和修正是减小误差的关键所在。本文所提出的定宽截断式并行乘法器产生的误差率较小,且适合于进行补码运算。另外,与标准的乘法器相比,几乎省去了一半的面积,具有更小的延迟时间,提高了运算速度。实验表明,这种截断式定宽乘法器与其他的定宽乘法器的运算结果相比,误差更小,且在面积的控制上也十分有效。

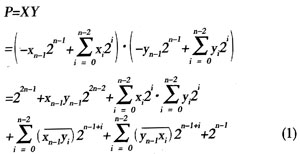

考虑乘法操作的两个N位的输入X和Y,经过一个标准的补码乘法器相乘后产生一位2N的输出为P。

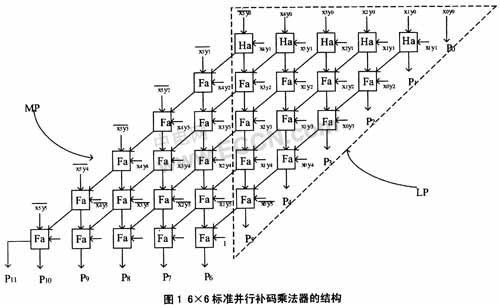

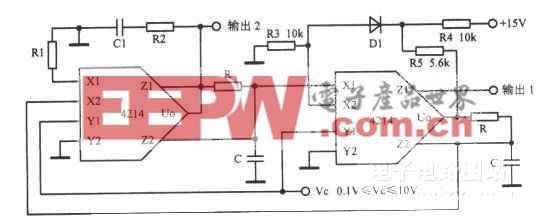

图1为6×6标准补码并行乘法器的架构。

定宽截断式乘法器的设计目标就是尽量减小与标准乘法器的输出误差,而关键的部分就在于截断处进位产生电路的设计。把产生乘法器进位的电路部分表示为Cg,根据公式(1)和图1所示的LP电路中,把以Pn-1行上所有的进位产生电路表示为αn-1,得到:

3、各种不同乘法器的误差率和面积比较

我们把标准的乘法器表示为MS,本文所提出的进位补偿的截断乘法器称MF,Kidambi et al.所提出的乘法器表示为M1,完全截断没有进行补偿的乘法器称为Mp,M2是由MP和其Pn-1位的行进位组成,但其进位全都输入为0。那么最大的绝对误差εM=|MP-FP|。平均误差:![]() ,为所有各个输出值的累加值。相对误差:εR=|MP-FP|/MP,PεR表示所有的输入相对误差εR的百分比大于0.01者,

,为所有各个输出值的累加值。相对误差:εR=|MP-FP|/MP,PεR表示所有的输入相对误差εR的百分比大于0.01者,

![]()

其他定宽截断的乘法器的PεR值和MF的PεR值的差定义为R,如果的值越小,则乘法器的精度越高。各种乘法器相比较的εM,ε,Pn-1的比较结果都列在表1中。结果表明MF的计算精度比其他的各种截断乘法器精度更高。

下面我们对各个乘法器面积进行比较,定义AN表示与非门和或非门的面积,AA表示与门和或门的面积,AH表示半加器的面积,AF表示全加器的面积。假定认为乘法器都由这些基本的部件所组成,且应用0.18μm工艺的标准单元库进行综合,得到如下结果:AH≌0.45AF,AA≌0.08AF和AN≌0.06AF。所得到的标准乘法器的面积和各个截断乘法器的面积之比,如表2所示。我们所提出的这种定宽截断乘法器的面积只有标准乘法器面积的将近一半,且比M2乘法器的面积还要小。

4、结语

以上论述了定宽截断式并行乘法器的实现研究,通过对截断部分的进位电路进行补偿可以有效的减小乘法器的输出误差,提高运算速度,在VLSI的实现中可以大大减小其面积。各种实验结论表明:使用这种乘法器在多媒体和DSP信号处理中可以大大减小芯片的面积,但对其性能无太大影响。

评论