采用高级节点ICs实现从概念到推向消费者的最快途径(08-100)

—— 采用高级节点ICs实现从概念到推向消费者的最快途径

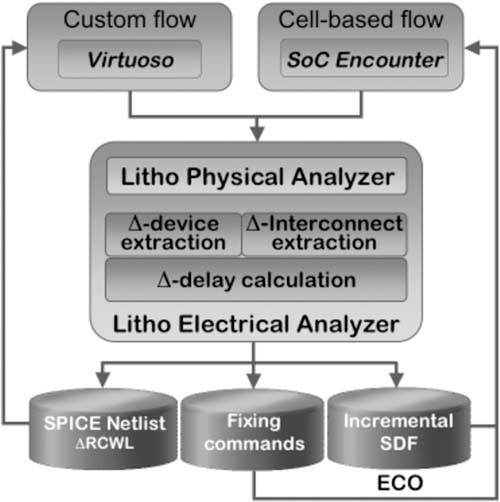

高级节点设计的要求已经导致物理设计签收的根本性变化。在45纳米设计中,设计规则检查(DRC)并不向设计师提供满足良品率要求的充分信息。半导体公司不能再期待在最后的DRC检查过程中的后期可制造性签收时,满足性能和良品率目标。与之前的签收阶段(例如时序签收和功率签收)不同,可制造性签收必须贯穿从概念到推向客户端整个开发过程,使用预防性措施和优化,避免代价高昂的芯片调试与重新设计如图2所示。

本文引用地址:http://www.amcfsurvey.com/article/91700.htm

图2 为了防止在开发后期出现代价高昂的问题,以及为了优化性能与良品率,半导体公司需要依靠精密的分析能力,并且将可制造性签收贯穿于从产品概念到消费电子设备成品的全过程。

应对越来越大的差异性

在以往的技术时代里,设计师可以设置余量以补偿简化的设计规则以及导孔问题和随机的极小缺陷造成的制造差异。而对于高级节点制造,设计师面临着扩大的体系与随机差异范围,出现了能够大大影响芯片性能的因素,用提高差数的方式已经无法有效弥补。在无法对这些影响进行建模并在设计初期采取预防措施的情况下,设计师会面临芯片的失败,而且没有多少可以纠正的后备选择。

电机保护器相关文章:电机保护器原理

评论