今天给大侠带来Xilinx FPGA编程技巧之常用时序约束详解,话不多说,上货。

基本的约束方法

为了保证成功的设计,所有路径的时序要求必须能够让执行工具获取。最普遍的三种路径以及异常路径为:

输入路径(Input Path),使用输入约束

寄存器到寄存器路径(Register-to-Register Path),使用周期约束

输出路径(Output Path),使用输出约束

具体的异常路径(Path specific exceptions),使用虚假路径、多周期路径约束

一、 输入约束Input Constraint

OFFSET IN约束限定了输入数据和输入时钟边沿的关系。

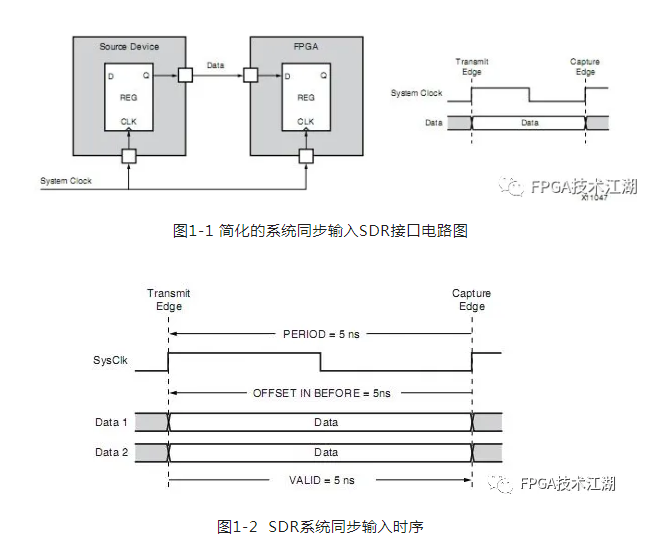

1. 系统同步输入约束System Synchronous Input

在系统同步接口中,同一个系统时钟既传输数据也获取数据。考虑到板子路径延时和时钟抖动,接口的操作频率不能太高。

上述时序的约束可写为:

NET "SysClk" TNM_NET = "SysClk";

TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%;

OFFSET = IN 5 ns VALID 5 ns BEFORE "SysClk";

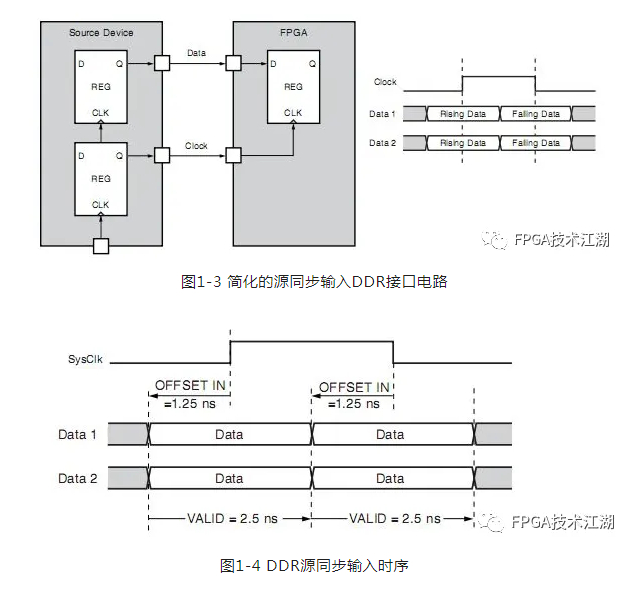

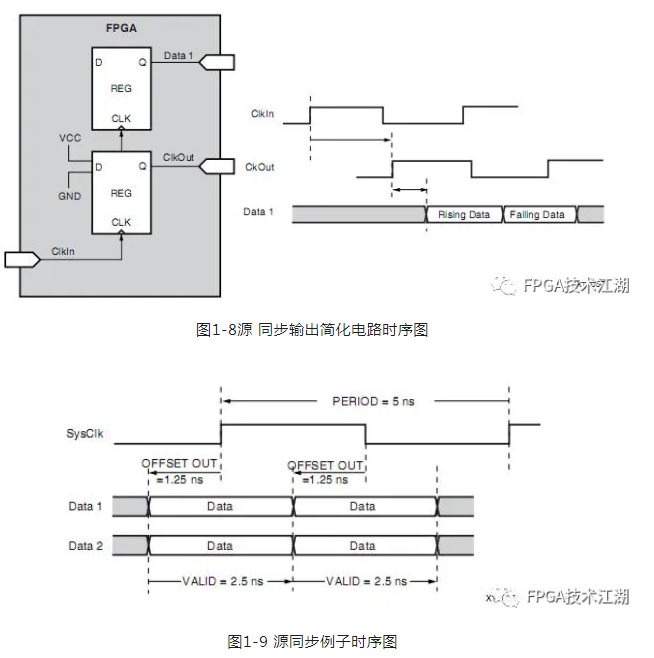

2. 源同步输入约束Source Synchronous Input 在源同步接口中,时钟是在源设备中和数据一起产生并传输。

上图的时序约束可写为:

NET "SysClk" TNM_NET = "SysClk";

TIMESPEC "TS_SysClk" = PERIOD "SysClk" 5 ns HIGH 50%;

OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "SysClk" RISING;

OFFSET = IN 1.25 ns VALID 2.5 ns BEFORE "SysClk" FALLING;

二、寄存器到寄存器约束Register-to-Register Constraint

寄存器到寄存器约束往往指的是周期约束,周期约束的覆盖范围包括:

覆盖了时钟域的时序要求

覆盖了同步数据在内部寄存器之间的传输

分析一个单独的时钟域内的路径

分析相关时钟域间的所有路径

考虑不同时钟域间的所有频率、相位、不确定性差异

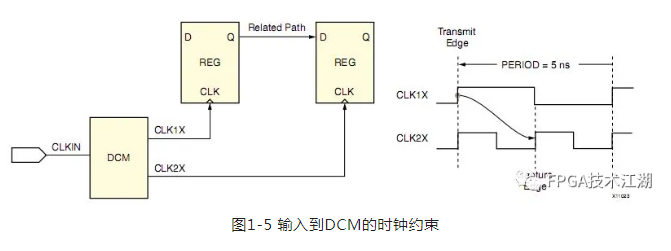

上图的时序约束可写为:

NET “ClkIn” TNM_NET = “ClkIn”;

TIMESPEC “TS_ClkIn” = PERIOD “ClkIn” 5 ns HIGH 50%;

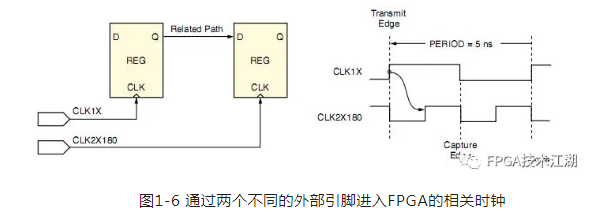

2. 手动约束相关联的时钟域

在某些情况下,工具并不能自动确定同步的时钟域之间的时钟时序关系,这个时候需要手动约束。例如:有两个有相位关系的时钟从不同的引脚进入FPGA器件,这个时候需要手动约束这两个时钟。

上图的时序约束可写为:

NET“Clk1X"TNM_NET=“Clk1X";

NET“Clk2X180"TNM_NET=“Clk2X180";

TIMESPEC"TS_Clk1X"=PERIOD"Clk1X 7 5ns;

TIMESPEC"TS_Clk2X180"=PERIOD"Clk2X180“TS_Clk1X/2PHAS2 +1.25ns;

3. 异步时钟域

异步时钟域的发送和接收时钟不依赖于频率或相位关系。因为时钟是不相关的,所以不可能确定出建立时间、保持时间和时钟的最终关系。因为这个原因,Xilinx推荐使用适当的异步设计技术来保证对数据的成功获取。Xilinx约束系统允许设计者在不需考虑源和目的时钟频率、相位的情况下约束数据路径的最大延时。

异步时钟域使用的约束方法的流程为:

为源寄存器定义时序组

为目的寄存器定义时序组

使用From-to和DATAPATHDELAY关键字定义寄存器组之间的最大延时

三、输出约束Output Constraint

输出时序约束约束的是从内部同步元件或寄存器到器件管脚的数据。

1. 系统同步输出约束System Synchronous Output Constraint

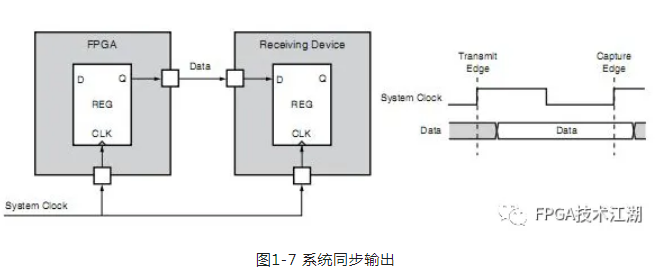

系统同步输出的简化模型如图所示,在系统同步输出接口中,传输和获取数据是基于同一个时钟的。

其时序约束可写为:

NET "ClkIn" TNM_NET = "ClkIn";

OFFSET = OUT 5 ns AFTER "ClkIn";

在源同步输出接口中,时钟是重新产生的并且在某一FPGA时钟的驱动下和数据一起传输至下游器件。

上述举例的时序约束可写为:

NET “ClkIn” TNM_NET = “ClkIn”;

OFFSET = OUT AFTER “ClkIn” REFERENCE_PIN “ClkOut” RISING;

OFFSET = OUT AFTER “ClkIn” REFERENCE_PIN “ClkOut” FALLING;

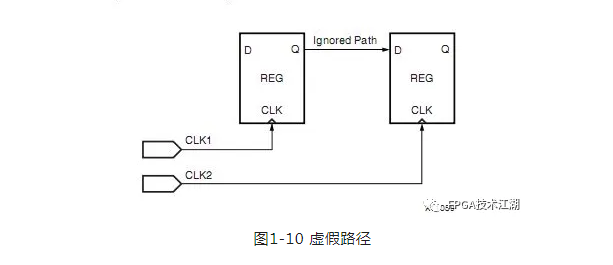

3. 虚假路径约束False Path Constraint

令SRC_GRP为一组源寄存器,DST_GRP为一组目的寄存器,如果你确定SRC_GRP到DST_GRP之间的路径不会影响时序性能,那么可以将这一组路径约束为虚假路径,工具在进行时序分析的时候将会跳过对这组路径的时序分析。这种路径最常见于不同时钟域的寄存器数据传输,如下图:

其约束可写为:

NET "CLK1" TNM_NET = FFS "GRP_1";

NET "CLK2" TNM_NET = FFS "GRP_2";

TIMESPEC TS_Example = FROM "GRP_1" TO "GRP_2" TIG;

在多周期路径里,令驱动时钟的周期为PERIOD,数据可以最大n*PERIOD的时间的从源同步元件传输到目的同步元件,这一约束降低工具的布线难度而又不会影响时序性能。这种约束通常用在有时钟使能控制的同步元件路径中。

必须说明的是上图Enable信号的产生周期必须大于等于n*PERIOD,且每个Enable传输一个数据。假设上图的n=2,MC_GRP为时钟使能Enable控制的多周期同步元件组,则约束可写为:

NET "CLK1" TNM_NET = "CLK1";

TIMESPEC "TS_CLK1" = PERIOD "CLK1" 5 ns HIGH 50%;

NET "Enable" TNM_NET = FFS "MC_GRP";

TIMESPEC TS_Example = FROM "MC_GRP" TO "MC_GRP" TS_CLK1*2;