Chirp函数的Nios Ⅱ嵌入式实现

摘 要:首先分析Chirp函数在频域上的一般特性,提出利用FPGA的嵌入式软核NiosⅡ处理器在嵌入式操作系统μC/OS-Ⅱ上实现Chirp的方法,即通过NiosⅡ处理器根据Chirp函数在频域上频率的跳变情况实时改变输出DDS(直接数字合成序列)模块的频率步进控制字的办法,控制DDS模块的频率输出,实现Chirp函数所要达到的扫频输出性的目的。通过在NiosⅡIDE编程环境中的Console窗口观察,该设计能很好地实现Chirp函数功能。

关键词:μC/OS-ⅡSoPC;DDs;FPGA;Chirp函数

0 引 言

SoC(System on(2hip)是20世纪90年代提出的概念,它是将多个功能模块集成在一块硅片上,提高芯片的集成度并减少外设芯片的数量和相互之间在PCB上的连接,同时系统性能和功能都有很大的提高。随着FPGA芯片工艺的不断发展,设计人员在FPGA中嵌入软核处理器成为可能,Altera和Xilinx公司相继推出了SoPC(System on a Programmable Chip)的解决方案,它是指在FPGA内部嵌入包括(;PtJ在内得各种IP组成一个完整系统,在单片FPGA中实现一个完整地系统功能。与SoC相比,SoPC具有更高的灵活性,FPGA的可编程特性使之可以根据需要任意定制SoC系统;与ASIC相比,SoPC具有设计周期短,设计成本低的优势,同时开发难度也大大降低。由于电磁波在传输过程中,经过色散介质如不均匀的波导,高空电离层时会发生色散现象,Chirp函数在射电天文信号的消色散处理中发挥着重要的作用,研究在FPGA中实现Chirp函数是基于FPGA的射电宇宙信号处理的重要组成部分。

l 系统总体设计

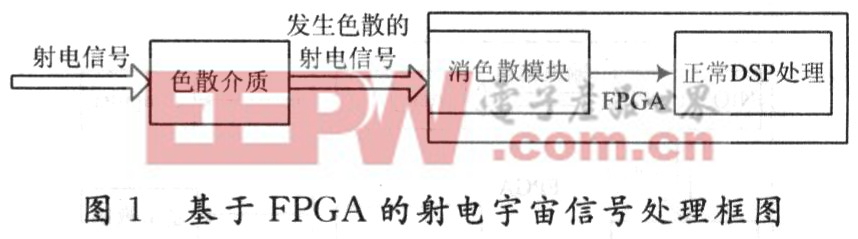

图1为基于FPGA的射电宇宙信号处理框图。

该设计是基于SoPC技术设计的Chirp函数信号发生器,该系统把微处理器模块和DDS模块集成到单片FPGA芯片内部,通过在嵌入式操作系统μC/OS-Ⅱ编写的程序,实时控制微处理器对DDS的控制字输出,DDS模块根据频率控制字的不同,输出不同的数字化正弦波。使之符合Chirp函数的时变频率特征。Chirp函数根据输出频率的递变规律一般分为两种:线性Chirp函数和非线性Chirp函数,以下是两种Chirp函数在频域上的表现图如图2,图3所示。

从图2,图3可以看出Chirp函数的频率输出与时间的f-t关系可以总结为:

(1)对于线性Chirp函数

在连续域时间域内有关系式:

![]()

式中:k为常数;f0为初始输出频率;t为连续时间。

在离散时间域有关系式:

![]()

式中:k为常数;f0为初始输出频率;n为采样点。

(2)对于非线性Chirp函数

在连续域时间域内有关系式:

![]()

式中:f为非线性函数;f0为初始输出频率;t为连续时间。

在离散时间域有关系式:

![]()

式中:f为非线性函数;f0为初始输出频率;n为采样点。

评论