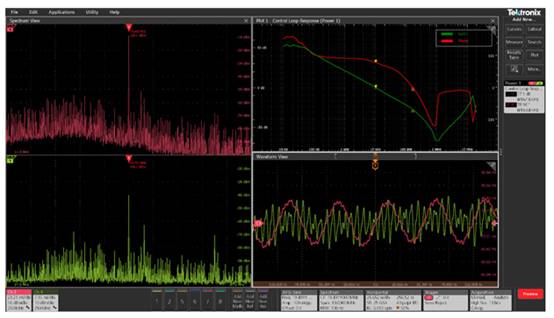

基于SoPC的数字示波器设计

摘要:在此提出一种基于SoPC的数字示波器设计。采用FPGA作为核心器件,通过硬件逻辑模块和NiosⅡ嵌入式处理器对高速A/D所采集的数据进行快速存储和处理,最终将波形还原显示在彩色液晶屏上。另外,还设计了用于PC机的软件以还原存储的波形信息,该软件同样也能够进行光标测量等操作。

关键词:数字示波器;SoPC;NiosⅡ;光标测量

0 引言

在电子技术领域中,示波器的应用非常广泛,使用它可以方便直观地观察到信号的全貌,并测量信号的幅度、频率、周期等基本参数。传统的模拟示波器显示时采用荧光物质的余辉时间都是一定的,导致其难以观测到周期较长的信号。另外,模拟示波器还无法对信号进行一些特殊的数学处理(如FFT)。而数字示波器正好可以克服模拟示波器的不足,它采用各种先进的测量技术来满足各种应用。如基于采样原理,采用高速A/D转换器实现高速数据采集,将模拟信号数字化,然后借助处理器强大的数据处理能力实现各种数字信号处理算法,将波形以图形的方式直观地显示出来,并能够得到被测信号各种丰富的参数。

1 系统总体方案

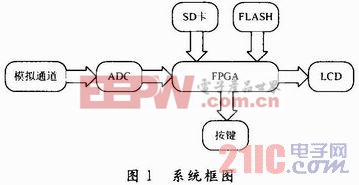

本设计的系统框图如图1所示,得益于FPGA的灵活性,系统的大部分功能都在FPGA内部完成,使得整体结构非常简洁。外围电路主要包括A/D转换模块、LCD显示器、SD卡、FLASH和按键。

A/D转换模块的功能是实现模拟信号到数字信号的转换;FLASH模块的功能是存储SoPC(System-on-a-Programmable-Chip)片上系统的固件程序;SD卡模块的功能是实现测量信息的长期、大量存储,提供与PC机的接口,便于后期在计算机上进行分析;LCD模块的功能是对测量信号波形和相关参数的实时显示;按键模块的功能是提供整机的调节和控制接口。

2 FPGA逻辑功能模块设计

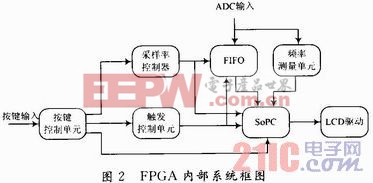

FPGA内部系统框图如图2所示。它主要由采样率控制器、触发控制单元、FIFO控制器、频率测量单元、按键控制单元和LCD驱动器构成。

评论