pcb设计逻辑芯片功能测试

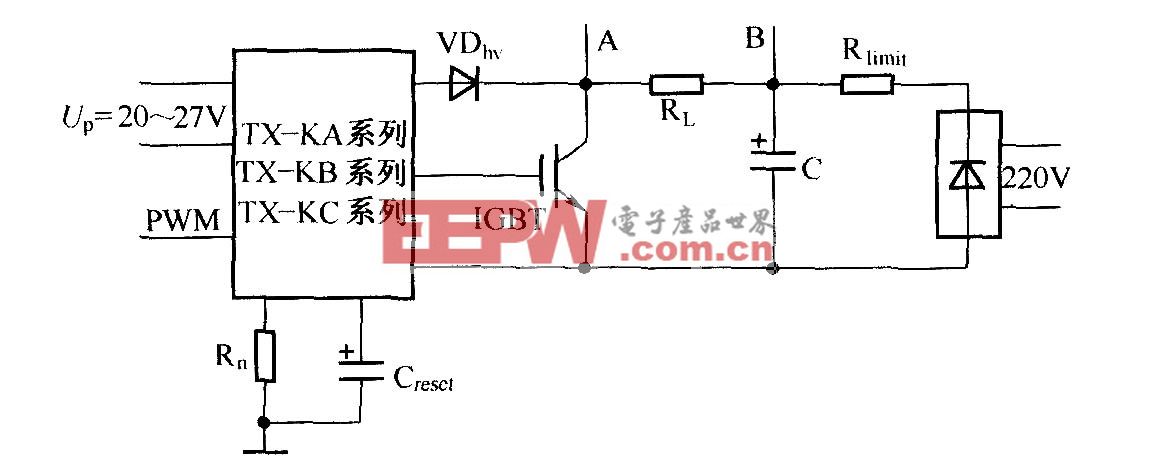

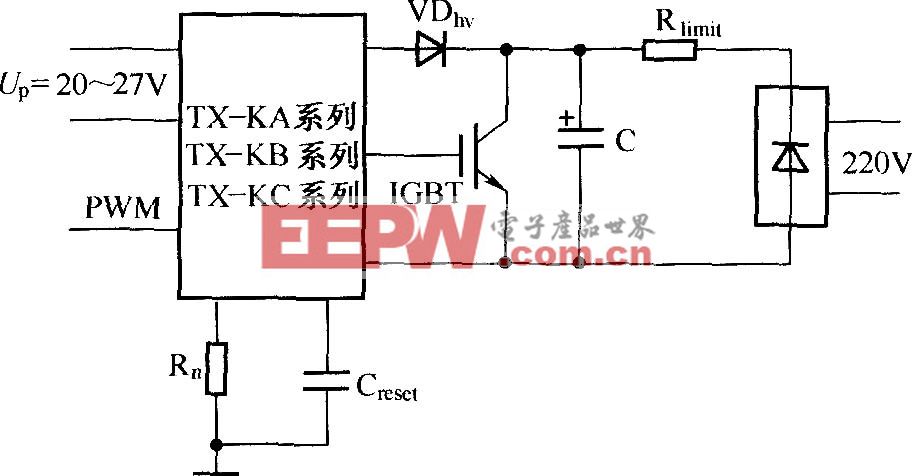

pcb设计逻辑芯片功能测试用于保证被测器件能够正确完成其预期的功能。为了达到这个目的,必须先创建测试向量或者真值表,才能进检测代测器件的错误。一个真值表检测错误的能力有一个统一的标准,被称作故障覆盖率。测试向量与测试时序结合在一起组成了逻辑功能测试的核心。pcb设计培训功能测试会占用测试系统的大部分资源。功能测试主要由两大块组成,一是测试向量文件,另外一块是包含测试指令的主测试程序。测试向量代表了测试待测器件所需的输入输出逻辑状态。主测试程序包含了保证测试仪硬件能产生必要的电压,波形和时序等所必需的信息。(如图一所示)

本文引用地址:http://www.amcfsurvey.com/article/190144.htm当功能测试执行的时候,测试系统把输入波形施加给待测器件,并一个周期一个周期,一个管脚一个管脚地监控输出数据。如果有任何的输出数据不符合预期的逻辑状态,电压或者时序,该测试结果被记录为错误。

到现在我们讨论了相对简单的存储器和数字芯片测试的基本测试技术。在此文接下来的两章里,我们将讨论测试更为复杂的混合信号和射频/无线芯片的独特要求。

测试向量

测试向量—也称作测试图形或者真值表—由输入和输出状态组成,代表被测器件的逻辑功能。输入和输出状态是由字符来表示的,通常1/0用来表示输入状态,L/H/Z用来表示输出状态,X用来表示没有输入也不比较输出的状态。事实上可以用任何一套字符来表示真值表,只要测试系统能够正确解释和执行每个字符相应的功能。

VDD Min/Max (待测器件电源电压)

VIL/VIH (输入电压)

VOL/VOH (输出电压)

IOL/IOH (输出电流负载)

VREF (IOL/IOH转换电平)

测试频率(测试使用的周期)

输入信号时序(时钟/建立时间/保持时间/控制)

输入信号波形格式

输出时序(在周期内何时对输出进行采样)

向量顺序(向量文件内的start/stop位置)

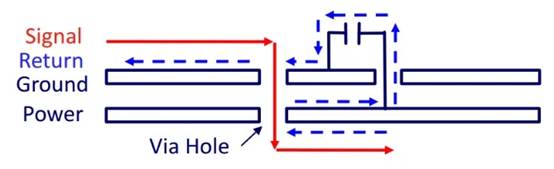

测试向量是存储在向量存储器里面的,每行单独的向量代表一个单一测试周期的“原始“数据。从向量存储器里输入的数据与时序,波形格式以及电压数据结合在一起,通过pin

electronic电路施加给待测器件。待测器件的输出通过pin

electronic上的比较电路在适当的采样时间与存储在向量存储器里的数据进行比较。这种测试被称作存储响应。

除了待测器件的输入输出数据,测试向量还可能包含测试系统的一些运作指令。比如说,要包含时序信息等,因为时序或者波形格式等可能需要在周期之间实时切换。输入驱动器可能需要被打开或者关闭,输出比较器也可能需要选择性地在周期之间开关。许多测试系统还支持像跳转,循环,向量重复,子程序等微操作指令。不同的测试仪,其测试仪指令的表示方式可能会不一样,这也是当把测试程序从一个测试平台转移到另一个测试平台时需要做向量转换的原因之一。比较复杂的芯片,其测试向量一般是由芯片设计过程中的仿真数据提取而来。仿真数据需要重新整理以满足目标测试系统的格式,同时还需要做一些处理以保证正确的运行。通常来说测试向量并不是由上百万行的独立向量简单构成的。测试向量或者仿真数据可以由设计工程师,测试工程师或者验证工程师来完成,但是要保证成功的向量生成,都必须对芯片本身和测试系统有非常全面地了解。

评论