利用FPGA实现外设通信接口之: 典型实例-字符LCD接口的设计与实现

10.8典型实例18:字符LCD接口的设计与实现

10.8.1实例的内容及目标

1.实例的主要内容

本节旨在设计实现FPGA与字符LCD的接口,帮助读者进一步了解字符液晶的工作原理和设计方法。

2.实例目标

通过本实例,读者应达到以下目标。

·学习字符型液晶显示器的控制原理。

·掌握利用FPGA设计驱动的基本思想和方法。

·熟练掌握状态机的使用。

10.8.2字符LCD接口实例内容

红色飓风开发板配套的字符液晶模块为2行,每行16个字符。本实要求显示功能如下:第一行显示“WelcomeRedLogicWorld!”,第二行显示“RedLogicWorld!”,由于一行只能显示16个字符,因此要整屏左移显示。

10.8.3FPGA代码设计实现

本设计的程序主要包含两个模块,一个模块为char_ram,另一个模块为LCD的驱动模块lcd。

char_ram模块的主要功能是根据输入的地址,输出相应字符在CGRM(字符存储发生器)中的地址。因为在控制LCD显示时,只需用户提供相应字符的地址,就可以显示出该字符。

在char_ram中,先设置好所有字符对应的地址,然后给需要用到的字符定义新的地址用于选择输出。

Lcd模块用于驱动lCD正常工作。LCD是一个慢显示器件,因此时钟一定要满足要求,在这里通过50MHz分频得到输入的时钟周期约为100µs(约10Hz),以满足慢显要求。LCD的驱动模块利用一个状态机来实现。具体程序参考实例源代码。

10.8.4ModelSim仿真验证

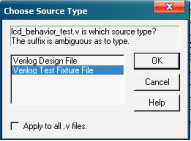

通过AddSource的方法直接将测试代码加入到工程当中。选中要加入的测试代码文件:led_behavor_test.v,弹出如图10.37所示的对话框,选择“VerilogTextFixtureFile”。

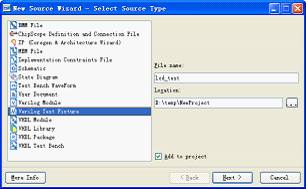

用户也可以直接新建一个仿真文件,选择“NewSource”,选择“VerilogTestFixture”,输入测试文件名称,如图10.38所示,单击“Next”按钮。

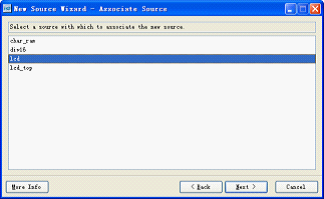

选择lcd模块(对哪个模块进行测试,就选择哪个文件),如图10.39所示。

图10.37选择源文件类型

图10.38新建仿真源文件

图10.39选择被测试模块

新建测试文件后,ISE会自动生成一部分代码,其余内容可直接从源工程中提供的测试文件中复制。

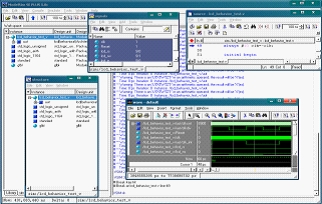

添加后选中测试文件可以看到如图10.40所示的信息。

图10.40仿真文件信息

在Processforsource下有4个M的图标,分别对应4个级别的仿真。从上至下,第一个为行为仿真,第二个为翻译后仿真,第三个为映射后仿真,第四个为布局布线后仿真。在这里先做行为仿真,只需双击第一个图标,就可启动ModelSim仿真,结果如图10.41所示。

图10.41行为仿真

默认情况下,ModelSim会弹出4个窗口,在这里主要观察Wave窗口,如图10.42所示。

图10.42行为仿真波形窗口

上面列出的很多信号是人为添加的,具体如何添加以及具体Wave窗口下的许多用法在这里不做详细叙述。需要特殊说明的是,如果用户自己装的是ModelSimXE版本,是无法完成这个仿真的,因为这个工程代码是用VHDL写的,测试代码是用Verilog写的,ModelSimXE版本是不支持混仿真的,建议安装ModelSimSE版本,SE下是支持混合仿真的。

ModelSim仿真结果如图10.43和图10.44所示。

图10.43LCD写数据仿真结果

图10.44LCD写指令仿真结果

这两个波形分别为写数据和写指令的仿真结果。写数据即向DDRAM写入要显示的字符对应的地址,其中clk为系统的输入时钟50MHz,clk_int为分频后得到的约10Hz输入时钟,lcd_e为使能信号,写数据时RS=1,R/W=0,写指令时RS=0,R/W=0。

10.8.5小结

本节对利用FPGA来驱动字符型液晶模块的方法做了介绍,并通过编译下载在红色飓风的开发板上实现了预定功能。

评论