东芝开发出带DNN的汽车级图像识别芯片(SoC)

2019年2月,东芝开发出一款汽车级图像识别芯片(SoC),与东芝上一代产品相比,该产品使深度学习加速器的速度提升10倍,功效提高4倍。由于新产品加入了深度神经网络(DNN)模仿大脑神经网络的算法,与传统模式识别和机器学习相比,DNN的识别处理精度要高得多,预计该产品将会在汽车领域得到广泛应用。这也是东芝目前最新的AI方向的产品。

本文引用地址:http://www.amcfsurvey.com/article/201905/400294.htm

值得一提的是,东芝的这项技术成果已于2019年2月19日在美国旧金山举行的2019 IEEE国际固态电路会议(ISSCC)上公之于众,并且新系统级芯片符合全球汽车功能安全标准ISO26262的要求。

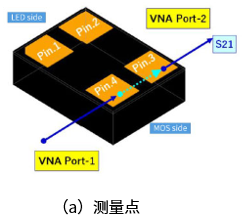

东芝通过在硬件上实现深度学习的DNN加速器解决了这一难题。它具有三大特点。

• 并行MAC单元。DNN处理需要大量MAC计算。东芝的新产品有四个处理器,每个处理器包含256个MAC单元。因此提高了DNN的处理速度。

• 减少了动态随机存取存储器(DRAM)存取。传统的系统级芯片没有本地内存,无法在靠近DNN执行单元的位置保存临时数据,并且在访问本地内存时会产生较大功耗。同时,加载用于MAC计算的加权数据也会产生较大功耗。东芝新产品可在DNN执行单元附近执行静态随机存取存储器(SRAM),并将DNN处理分为多个子处理块,因此可将临时数据保存在SRAM内,从而减少了DRAM存取。此外,东芝还在加速器上增加了一个解压缩单元。可通过解压缩单元加载预先压缩并存储在DRAM中的加权数据。因此,降低了加载来自DRAM的加权数据时产生的功耗。

• 减少了SRAM存取。传统深度学习需要在处理DNN的每一层之后访问DRAM,因此功耗过高。该加速器在DNN的DNN执行单元中设计有管线层结构,以便在一次SRAM存取期间执行一系列DNN计算。

评论