基于SOPC的嵌入式高速串口设计(06-100)

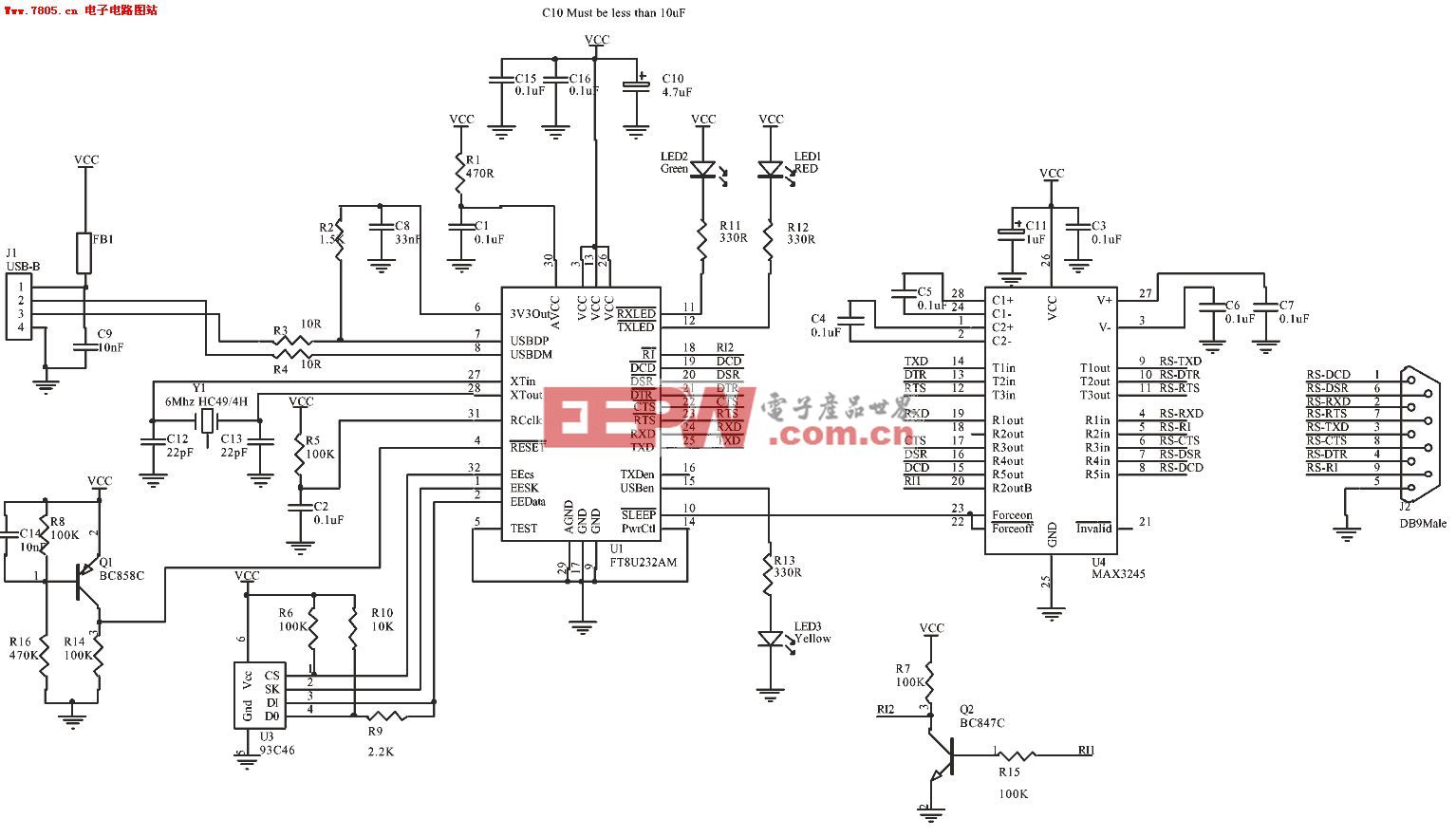

无论是主机模块还是外围模块均采用相同的串口通信设计,串口通信设计包含两个主要部分:通信接口部分和管理控制部分。通信接口部分主要完成数据帧结构的封装和解封装,并通过帧头的分析识别进行时隙定位,同时能让系统内的每一终端实现多机共享通信资源的通信机制,该模块由VHDL语言实现。管理控制部分由NiosII软核实现的,为了能在串行通信方式上实现时分复用,进而实现多设备同时通信,系统设计出一套完整而独特的控制帧格式,并通过这些帧格式控制实现建立连接,撤销连接和相应管理。因此,利用NiosII的特点,形成特殊的帧头判决、同步时钟提取、控制信息的判断、收发模式变换,这些都依赖专用模块的实施并靠高速执行速度来适应多终端下的高传输速率。

本文引用地址:http://www.amcfsurvey.com/article/81083.htm鉴于以上系统架构和设计要求,串口通信采用模块化设计思路和方法,模块结构如图2所示。

NiosII软核CPU开发工具SOPC Builder提供简洁的操作方式,可将用户的数字电路模块封装成标准的NiosII软核外设模块,这使得NiosII软核可以很容易地与用户逻辑结合,构成功能更加强大的SOC系统。在高速串口数据通信的设计中,既需要一个高速的处理器作为系统的控制管理核心,又有大量用户自定义的数字电路功能模块需要在FPGA芯片中实现,因此,采用FPGA芯片和NiosII软核CPU作为高速串口数据通信的硬件平台是一个优化的选择。

通信接口模块设计

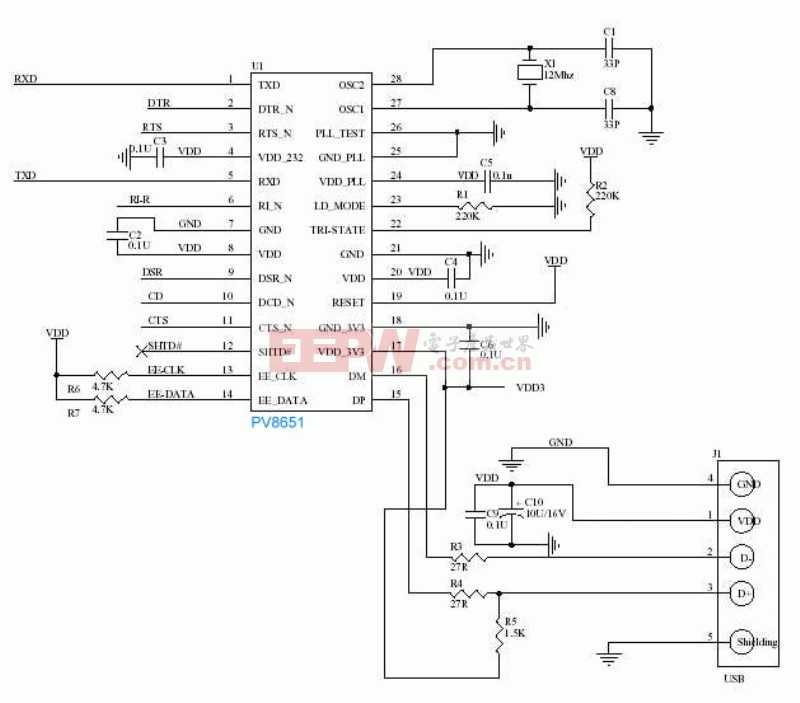

通信接口模块设计采用VHDL语言设计,由两部分组成:数据帧发送电路和数据帧接收电路。数据帧发送电路将NiosII 要发送的数据、地址按照数据帧格式进行组帧,然后同步传输到总线上,该部分设计的关键是并串转换、合并数据和同步控制,数据的发送率为5Mbits/s,而工作时钟fclk为25MHz,对fclk进行5分频,得发送时钟ftxd为5MHz。当有数据要发送时,每一个即ftxd的上升沿到来时传送数据,先发送帧头2字节引导序列,即“1110011100111110”,然后发送串行数据。由于NiosII的内部数据宽度通常是32位,故将1字节地址和3字节数据由软件将其合并成一组32位宽度的数据,合并时地址在低位,数据在高位,然后将要发送的32位数据缓存在一个32位宽度的矢量区间,引导序列结束后从低位到高位依次发送数据,即data[0]、data[1]……data[31],最后发送结束标志字节“1110011”,发送结束。

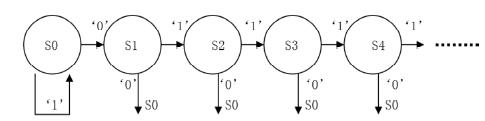

接收电路的设计重点考虑的问题是如何准确判断到数据帧头,然后解析地址,数据的速率为5Mbit/s,FPGA的工作时钟fclk为25MHz,参考RS-232串口通信的设计思想,用高倍时钟对接收的数据进行采样,即每5个fclk采样一个bit,此处可以先设计一个5进制计数器,每一次计数,保存采集的数据,在第2、3、4次采样时,若所采到的值相同,则判断这个bit为当前的采样值。在判断2字节引导序列时采用状态机设计法和序列检测器的设计思想,判断第1个bit是否为‘0’,如果是‘0’则继续判断下一bit是否为‘1’,如果是‘1’则一直等待在第1状态直到判断到‘0’才跳转,判断状态机如图3所示。

评论