基于SOPC的嵌入式高速串口设计(06-100)

用户定义的Avalon总线模块设计

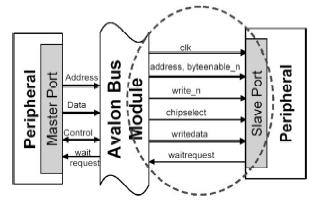

本文引用地址:http://www.amcfsurvey.com/article/81083.htm NiosII是基于RISC技术的通用嵌入式处理器芯片软内核,它特别为可编程逻辑进行了优化设计,也为可编程单芯片系统设计了一套综合解决方案。Avalon总线是一种高效的总线结构,主要用于连接片内处理器NiosII和各种外设IP core,以构成可编程系统芯片(SOPC)。数据帧发送电路和数据帧接收电路通过Avalon总线和NiosII处理器连接在一起,Avalon总线规范定义了主端口和从端口之间通过Avalon总线模块传输数据所需的信号和时序。设计时通信模块采用从端口传输模式,数据帧发送电路采用具有外设控制等待周期的从端口写传输模式,发送电路除串行数据输出线外,还必须提供符合Avalon总线传输要求的信号线,即Address、Writedata(31..0)、Write_n、Chipselect、Waitrequest,与NiosII工作同步的时钟信号clk,当CPU要发送数据时,将Address、Write_n信号有效,同时将要发送的32位数据装载到Writedata(31..0)上,而同步时钟clk一直处于工作状态,当clk上升沿判断到以上信号有效后,Avalon总线对Address译码,然后置Chipselect有效,而发送电路VHDL程序设计时必须判断Address、Chipselect是否有效,如果有效,则在下一个clk上升沿前将Waitrequest置为无效,数据传送电路就从Avalon总线获取Writedata数据,如果Waitrequest有效,则这个总线周期就成为等待周期,其他信号以及数据信号保持不变,但外设必须保证不会使Waitrequest无限期地保持有效,这样会使得一个从外设能够将Avalon总线永久“挂起”,其连接关系和时序关系如图4所示。同理,数据接收电路采用具有外设控制等待周期的从端口读传输模式,可以将串转并后的数据送入到NiosII中进行处理。

软件设计

基于NiosII的C语言设计,可以采用单线程模式,也可采用uc/基于NiosII的C语言设计,可以采用单线程模式,也可采用uc/OSII多任务操作系统。这里对接收和发送的数据处理主要采用以下指令实现,“IORD(base, 1)”读指令,其中base就是需要读取的外设基地址,数据接收电路作为外设在建立SOPC Builder时定义的名称为“user_uart_rxd”,则base应改为“user_uart_rxd_base”,而第2个参数‘1’表示其偏移地址;“IOWR(base, 1, data)”写指令,其中base是需写入外设基地址,数据发送电路作为外设在建立SOPC Builder时定义的名称为“user_uart_txd”, 则base应改为“user_uart_txd_base”,而第2个参数‘1’表示其偏移地址,第3个参数data是发送数据。

计算机仿真波形如图5、图6所示。它们之间的时序关系参照本文的第二部分。

结语

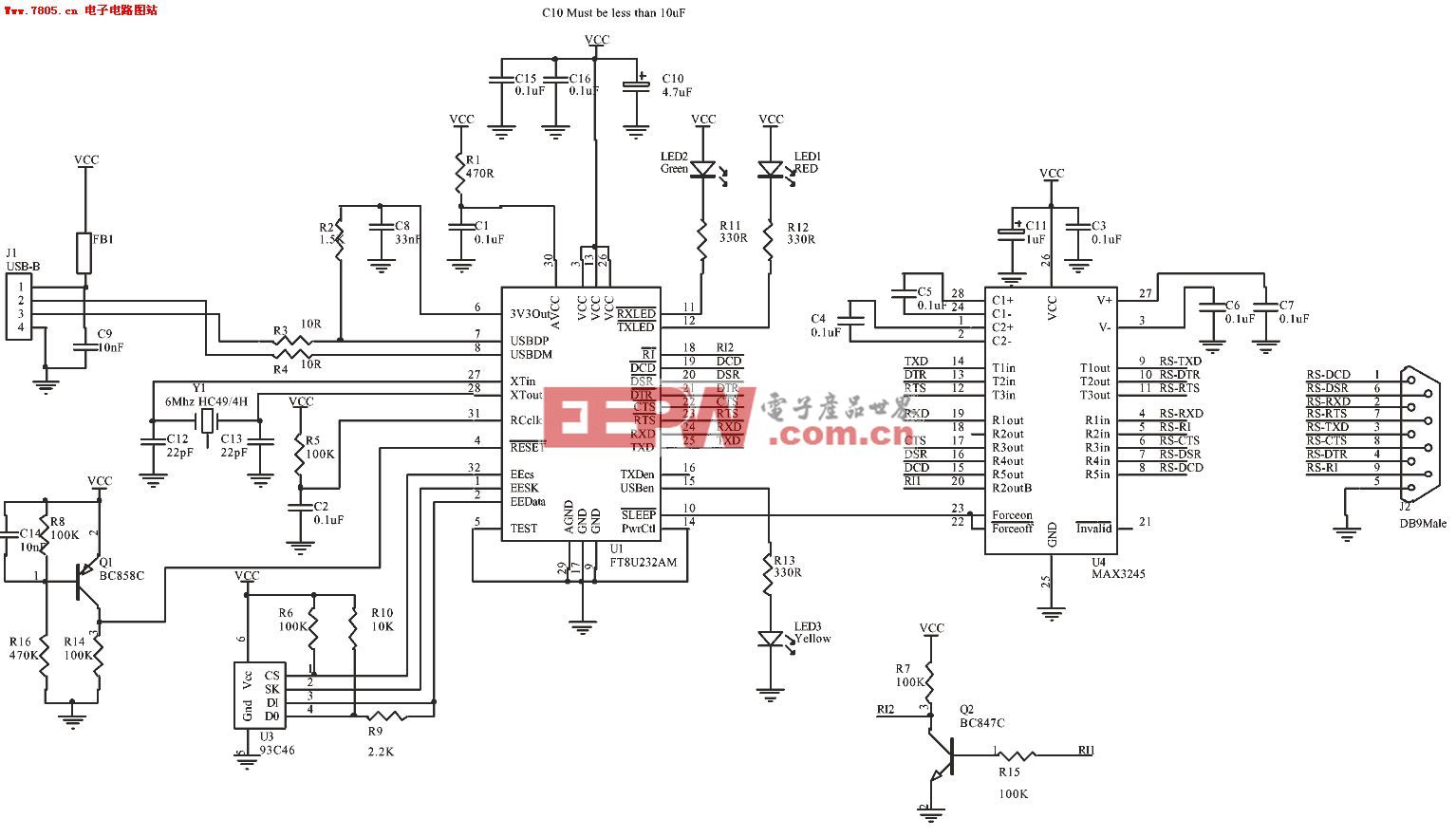

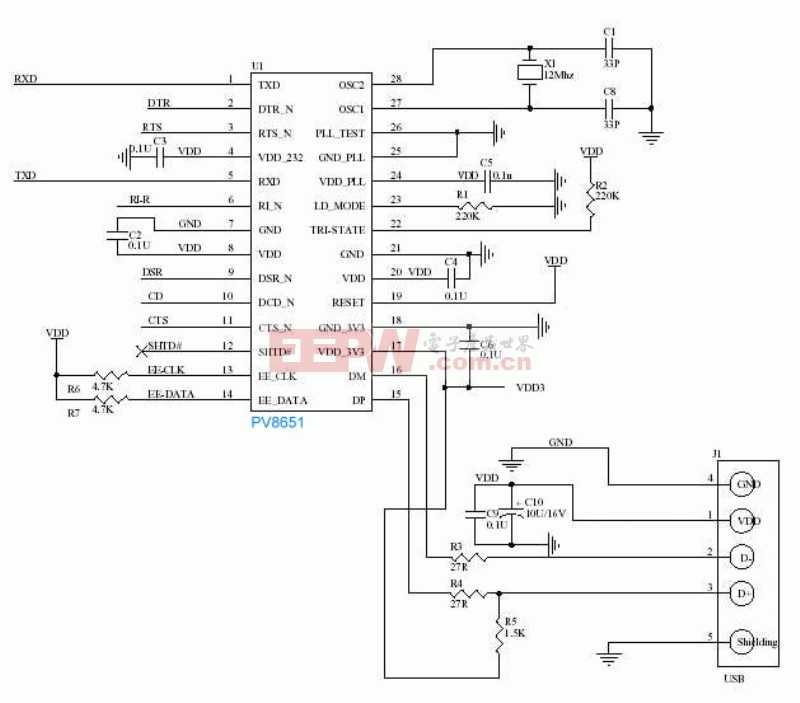

运用此5Mbit/s的UART进行通信,效果十分稳定、可靠性高,传输速度快,采用RS485接口模式传输距离远,同时不易被干扰以至出现误码、丢数据、丢帧等情况。因此采用SOPC嵌入式系统设计技术可以实现系统设计的小型化、集成化和高可靠性,还可以减少风险、降低成本、缩短开发周期。

linux操作系统文章专题:linux操作系统详解(linux不再难懂)

评论