AVR和TMS320VC5402的HPI接口通信设计

1.引言

本文引用地址:http://www.amcfsurvey.com/article/171954.htmTMS320VC5402(简称VC5402)是TI公司的DSP处理器,具有高级的数据处理结构和丰富的片内资源。但是VC5402 DSP内部不具有可编程的非易失片内存储器,所以为了保存程序代码和参数表,一般情况下要外扩一片存储器。VC5402可用的通用输入输出口(I/O port)少,软件上对I/O口的控制不灵活,没有对I/O口按位控制的指令,且具有流水线延迟。多不具有通用的通信接口如UART接口,CAN总线接口等,对控制的支持功能较少。AVR(Advanced RISC Architecture)单片机是ATMEL公司的flash型单片机,广泛应用于数据处理和控制领域,具有丰富的片内资源和灵活的接口形式。片内往往集成了几十kB乃至几百kB的flash存储器,每个端口几乎都可以通过软件设置为通用的I/O口和具有特殊功能的端口。将AVR单片机和VC5402处理器相结合,发挥各自的优点将是一个很好的设计方案。本文详细描述了AVR型单片机ATMEL64L和VC5402的HPI接口的硬件设计原理和软件设计构架,同时详细阐述了VC5402 HPI形式的bootloader方法及AVR实现方法。

2. 硬件设计原理

2.1. VC5402的HPI接口

VC5402的HPI接口是一个增强版的8位并行的HPI接口简称为HPI-8[1]。在 HPI-8接口中VC5402是从机。主机可以访问VC5402中位于0x60~0x3FFF存储器空间的片内存储器,这一区域是VC5402用户可用的所有的片内存储器资源。主机通过两个寄存器:地址寄存器(HPIA)和数据寄存器(HPID)访问VC5402内部的存储器。还有一个控制寄存器(HPIC)包含有控制和状态信息。HCNTL[0..1]是HPIA、HPID和HPIC的选址信号。同时,VC5402对 HCNTL[0..1]=“01”设置了特殊的访问模式以加快主机访问片内存储器的速度。此时主机读写HPID的内容不用每次设置HPIA,当主机读 HPID时VC5402将当前HPIA所指出的片内存储器的数据传送到HPID寄存器,同时HPIA的内容减1,当主机写HPID时DSP先将当前 HPIA的内容加1,然后由此时HPIA所指出的片内存储器的数据传送到HPID寄存器。由此可见此种方式比较适合于主机访问DSP内部的连续存储器空间。由于DSP内部是按着16位的数据进行组织,所以主机通过8位的HPI口进行读写操作都必须由两次操作组成,在两次操作中由HBIL信号标明高低位字节。

2.2. ATMEL64L简介

AVR单片机是ATMEL公司的8位高性能的低功耗微控制器。具有高级的精简指令集结构,绝大多数指令都是单周期指令,执行速度快。ATMEL64L是 Atmega103的升级版,具有64k字节在线可编程的flash存储器,可用于存储程序和固定的数据。具有2k字节的EEPROM,位于数据区,可用于保存参数表。具有4k字节的SRAM,为动态数据结构的存储建立了可能。丰富的指令集、大容量而多样的存储器结构增加了ATMEL64L程序设计的灵活性。另外ATMEL64L还具有丰富的片内外设,诸如:USART、SPI、定时器/计数器、PWM通道、在片的模拟比较器等,提供了丰富的通信及控制资源。

2.3. 硬件设计实现

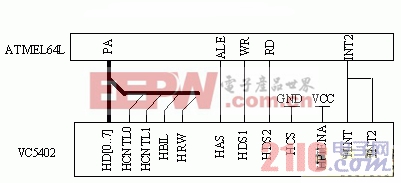

ATMEL64L和TMS320VC5402的HPI-8接口的硬件设计关键在于实现HPI-8接口的逻辑时序。我们研究ATMEL64L外部数据空间的读写时序[2]和HPI-8接口时序[1]发现:AVR的ALE信号在下降沿锁存低8位地址信号(DA7:0),而HAS信号也是在下降沿锁存HCNTL[0..1]、HBIL和HRW信号。在 AVR的WR信号的上升沿数据总线上的数据DA7:0已处于有效状态,在RD信号的上升沿来临时数据总线的数据DA7:0必须处于有效状态,同时HPI- 8的两个数据存储信号HDS1和HDS2均是在上升沿将相应的寄存器内容设置到HD[7..0]上或是将HD[7..0]的数据锁存到相应的寄存器。由此可见HPI-8的重要控制线均可以和AVR相应的控制线直接相连而不需要其他逻辑电路。设计的电路原理图见图1。

图1 电路原理图

当DSP退出复位状态后,30个有效时钟周期内触发了一个有效的DSP中断2,则DSP将仅进入HPI的 bootloader加载方式。原理图中将HINT引脚和DSP INT2引脚直接相连就是为了DSP复位后实时的触发DSP INT2中断。VC5402通过ATMEL64L的INT2中断申请加载DSP程序

3.HPI bootloader方式的实现

3.1. DSP bootloader方式简介

DSP的bootloader模式就是将DSP的程序代码和参数表由存储位置移动到运行位置。之所以采用这一方式主要出于以下几方面的考虑:

1.DSP系统的运行速度很快,如果程序代码存储在访问速度较慢的非易失存储器,将严重影响数据处理的速度。为提高效率有必要将程序代码移动到快速的存储空间[3]。

2.将程序代码存储位置和运行位置分开将有利于软件的在线升级。

VC5402的片内ROM存储器0xF800~0xFBFF中有TI公司固化的bootloader程序[3][4]。当VC5402处于微计算机模式时,其复位后首先执行bootloader程序。Bootloader程序依次扫描各种加载方式,当某一种方式满足时,程序停止扫描,开始以此种方式加载DSP程序。这里我只介绍HPI方式的bootloader,其他方式的bootloader加载方法请参考[5-7]。当DSP查询到有INT2中断发生时就进入HPI方式的bootloader,清零0x007F存储器单元,设置HINT信号向主机发送中断请求。查询 0x007F单元的内容是否为零,当不为零时表明DSP程序加载完毕。将0x007F单元的内容作为程序的入口地址开始执行加载的DSP程序。

3.2.HPI bootloader方式的软件实现框架

通过CCS将DSP源程序编译连接成COFF文件格式得到.out文件。然后,由.out文件获得DSP代码的二进制文件。在AVR的C语言编辑环境ICCAVR V6.30C中采用下述方法将DSP的代码数据配置到AVR flash空间。要注意const关键字使用。

/* dsp vector section data. start address = 0x1000, length = 0x78 */

const unsigned int vector[120]={0xF073,0x3000,…,0xF495};

当DSP进入HPI Bootloader方式时,AVR的外部中断2产生。AVR响应外部中断2传输完相应的数据段到DSP对应的片内存储器后要撤销DSP的中断申请。软件框架如下:

评论